Formal Aspects of Computing

# Fault trees on a diet: automated reduction by graph rewriting

Sebastian Junges<sup>1</sup>, Dennis Guck<sup>2</sup>, Joost-Pieter Katoen<sup>1,2</sup>, Arend Rensink<sup>2</sup> and Mariëlle Stoelinga<sup>2</sup>

<sup>1</sup> Software Modeling and Verification, RWTH Aachen University, Aachen, Germany

<sup>2</sup> Formal Methods and Tools, University of Twente, Enschede, The Netherlands

**Abstract.** Fault trees are a popular industrial technique for reliability modelling and analysis. Their extension with common reliability patterns, such as spare management, functional dependencies, and sequencing—known as *dynamic* fault trees (DFTs)—has an adverse effect on scalability, prohibiting the analysis of complex, industrial cases. This paper presents a novel, fully automated reduction technique for DFTs. The key idea is to interpret DFTs as directed graphs and exploit graph rewriting to simplify them. We present a collection of rewrite rules, address their correctness, and give a simple heuristic to determine the order of rewriting. Experiments on a large set of benchmarks show substantial DFT simplifications, yielding state space reductions and timing gains of up to two orders of magnitude.

Keywords: Fault tree analysis, Dynamic fault trees, Reliability, Graph rewriting.

# 1. Introduction

Since the 1970s, probabilistic safety assessment is a well-established technique to numerically quantify risk measures in safety-critical systems. It aims at determining the scenarios that lead to a system failure, assesses their likelihood, and yields information about the causes of these system failures. Typical measures of interest are the system reliability (i.e., what is the probability that the system is operational up to time t?) and availability (i.e., what is the probability that the system is operational up to time t?) and availability (i.e., what is the expected up time?). Fault tree analysis [SVD<sup>+</sup>02] is one of the most prominent safety assessment technique. It is standardised by the IEC [IEC07], and deployed by many companies and institutions, like FAA, NASA, ESA, Airbus, Honeywell, etc. Fault trees (FTs) model the various parallel and sequential combinations of failures of the various system components that ultimately may lead to an undesired event (e.g., core damage); for a recent survey see [RS15]. FTs model how failures propagate through the system: the leaves model individual component failures or human errors and are equipped with continuous probability distributions describing the random failure behaviour of the component. The internal nodes of an FT—referred to as gates—model how component failures lead to system failures.

Correspondence and offprint requests to: S. Junges, E-mail: sebastian.junges@cs.rwth-aachen.de

**Static fault trees.** Typical gates in static FTs are logical gates such as AND and OR-gates. Due to, e.g., redundancy, not every single component failure leads to a system failure. The probability distributions of the leaves are propagated in a bottom-up fashion through the tree according to the logic of the gates to reach a probability distribution of the top event, the root of the FT. The analysis of static FTs is rather straightforward as only logical gates are used (without negation), and thus gates have no internal state. Most analysis techniques for static FTs are based on determining the minimal cut sets (MCSs), the set of minimal failure combinations that lead to the top event failure. This can be efficiently done by succinct data structures such as binary decision diagrams (BDDs). The probability calculations are then carried out on top of this logical analysis using the MCSs.

**Dynamic fault trees.** Dynamic fault trees (DFTs) [DBB92, SVD<sup>+</sup>02] are directed acyclic graphs that are more expressive and more involved than static fault trees. They cater for common dependability patterns, such as spare management, functional dependencies, and sequencing, see also [JGKS16], and have in common that their behaviour is dynamic, that is, their behaviour not only depends on the set of failed components, but possibly also their order. Besides the logical gates as in static FT, DFTs feature gates that have more involved behaviour. For instance, the PAND-gate fails if all its children have failed in a left-to-right order; if this ordering is violated, the PAND does never fail; it is so-called fail-safe. The treatment of spare components (such as spare tires in a car) is modelled by a SPARE-gate. If its child, the component at hand, fails, it can be replaced by its spare; if that spare also fails, and there are no other spares left, the SPARE gate fails. Though this behaviour seems relatively simple at first sight, the fact that spare components may be shared by various SPARE gates, and may themselves be DFTs (and not just leaves), complicates matters considerably. It is commonly assumed that component failures are governed by negative exponential distributions. Though this is sometimes a simplification, this abstraction is well-suited in cases only mean values of failure rates are known. (Technically speaking, the distribution that maximises the entropy whenever only the mean value  $1/\lambda$  is known is the exponential distribution with rate  $\lambda$ .) Thus, the DFT behaviour is described by continuous-time Markov chains (CTMCs), where transitions correspond to the failure of a basic event.

The analysis of DFTs relies on extracting an underlying stochastic model, such as a Bayesian network [BPMC01, BD06], a (variant of a) CTMC [DVG97, BCS10] or a stochastic Petri net [Rai05, BFGP03] whose semantics is a CTMC too. The state-of-the-art techniques rely on generating CTMCs. The *state space generation* process—how to obtain a representation of the CTMC—is one of the main bottlenecks in DFT analysis. In fact, the analysis time is typically only a small part of the DFT analysis. The major cause is the internal state of DFT gates. For instance, for a PAND-gate one needs to keep track in which order children fail, while for a SPARE-gate the status of the spare components (are they in use or not, or even failed themselves?) and the order of the spare components (in case a SPARE has more than single spare component) needs to be administered. This altogether may yield huge state spaces. The technique advocated in this paper aims at boosting this process by simplifying DFTs prior to their state-space generation.

State of the art. An effective technique to keep the state space generation process manageable is to generate the CTMC in a *compositional* manner. The idea to apply this principle to DFTs goes back to Boudali et al. [BCS10] and basically works as follows. For each leaf and each gate of the DFT a CTMC is generated. As those behaviours affect only a single gate or leaf, these state spaces are relatively small. The individual CTMCs are then composed in parallel. In order to do so, the CTMCs are equipped with actions that can be used to synchronise them with CTMCs of other components. (This yields so-called interactive Markov chains [Her02], a mixture of labelled transition systems and CTMCs.) The compositional state space generation is done by considering pairs of CTMCs, reducing their state space by means of bisimulation—a.k.a. lumping—and composing the result with the next CTMC. This process is continued until a single CTMC is obtained. In this way, the peak memory consumption is not the state space of the entire CTMC, but the maximal size of the pairs of lumped Markov chains. As shown in Boudali et al. [BCS10], this mostly yields a compact state space. This approach is supported by the tool DFTCalc [ABvdB<sup>+</sup>13]. The DFT measures of interest such as system reliability and availability can then be established by standard means such as probabilistic model checking techniques for CTMCs [BHHK03].

**DFT rewriting.** The key idea of the approach in this paper is to *rewrite* a DFT prior to the state space generation. The rewriting is aimed to simplify a DFT by turning it into an equivalent DFT with a smaller state space. For static FTs, such rewriting can simply be done by adopting rules from Boolean algebra, e.g.,  $(x \land y) \lor (z \land y)$  is equivalent to  $(x \lor z) \land y$ . BDDs in fact yield compact canonical representations in many cases, i.e., the reduction is effectively done using the BDD representation.

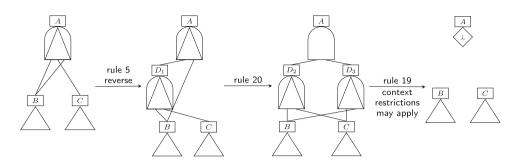

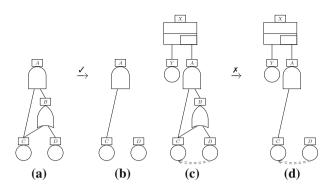

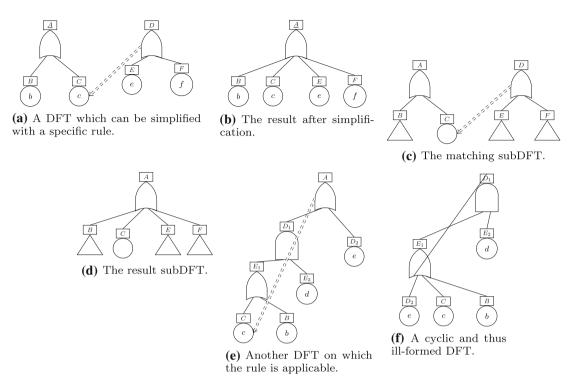

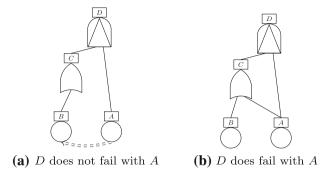

Fig. 1. An example of a simple rewriting of a DFT with conflicting ordering constraints

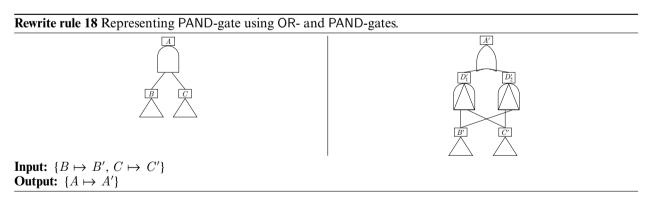

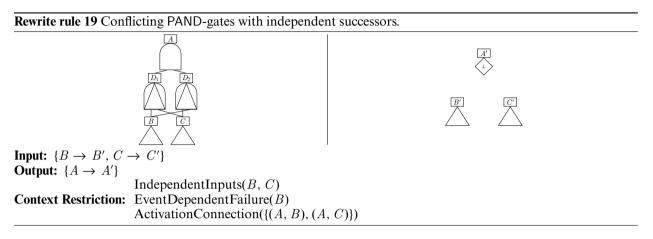

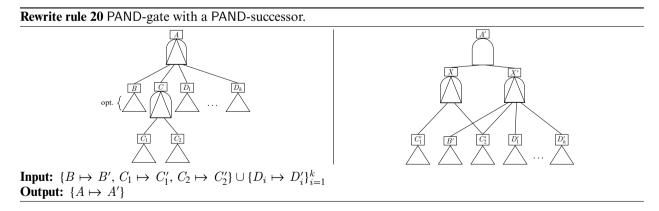

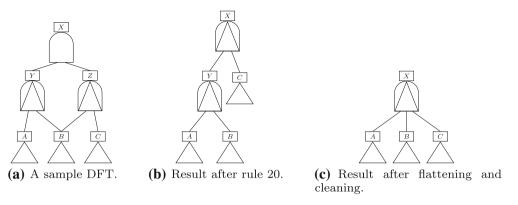

Rewriting DFTs is however more involved. This is due to the fact that the ordering of failures needs to be respected and the internal state of gates is relevant. To tackle these difficulties, we resort to graph transformation. The core idea is to consider DFTs as (typed) directed graphs and manipulate them by graph transformation [EEPT06], a powerful technique to rewrite graphs via pattern matching. A small example illustrates this idea. Consider the leftmost DFT in Fig. 1, where the top level event is a PAND-gate, and the children B and C represent arbitrary DFTs. This DFT is fail-safe, as the DFT requires B to fail before C, and C to fail before B. Our rewrite rules allow for rewriting this DFT into a DFT which is represented as  $\perp$ , see the rightmost DFT in Fig. 1. This is done in three rewrite steps. In the first step, the original PAND with three children is replaced by two binary PAND-gates. Though this introduces a new gate, it allows for a further simplification in the last step. The second rewrite step introduces an AND-gate as top event with two PAND-gates as child. This represents that the original DFT is indeed a conjunction of two conflicting orderings. The final rewrite step exploits this and results in the fail-safe DFT. As this rule is only correct provided the sub-DFTs B and C have no common elements, the latter rewrite step is subject to a context restriction.

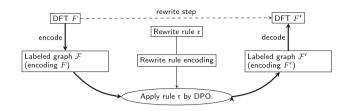

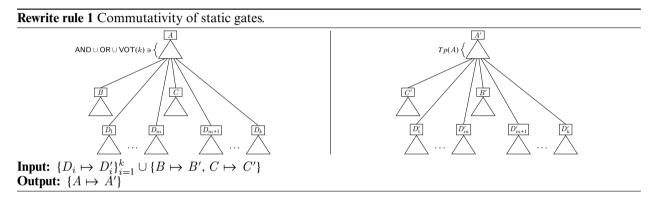

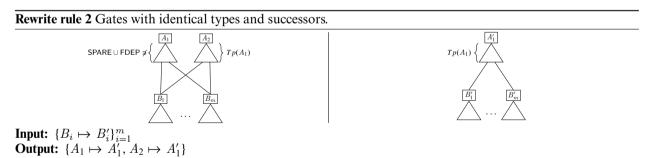

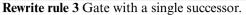

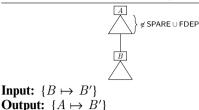

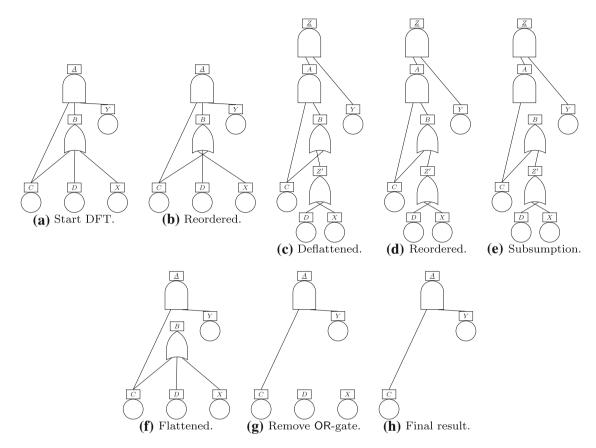

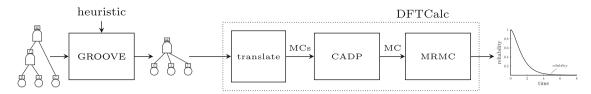

We present a catalogue of 29 (families of) rules that rewrite a given DFT into a smaller, equivalent DFT. Here, equivalence means that the source and target DFT have the same system reliability and availability. Thus, the probability of the top level event failing within a given deadline as well as the mean time to failure for the top level event are preserved by our rewriting rules. In contrast to reduction rules for static FTs, various rewrite rules for DFTs are context sensitive and benefit from the powerful framework of graph transformations. (Even relatively simple rules like the elimination of children of an OR-gate that cannot fail, require context conditions). As the rewrite rules can often be applied in two directions, some guidance in the selection of rules is required. For instance, in the above example, it is of no use to apply the reverse of the first rewrite rule on the second (from the left) DFT. Note that our rewrite system is not strongly normalising, i.e., it is not the case that every sequence of rewrites terminates with an irreducible DFT. We use a simple heuristic which determines the order to apply the rewrite rules. Our empirical evaluation shows that this simple heuristic is already very effective. Figure 2 provides an overview of how DFT rewriting exploits standard graph transformation.

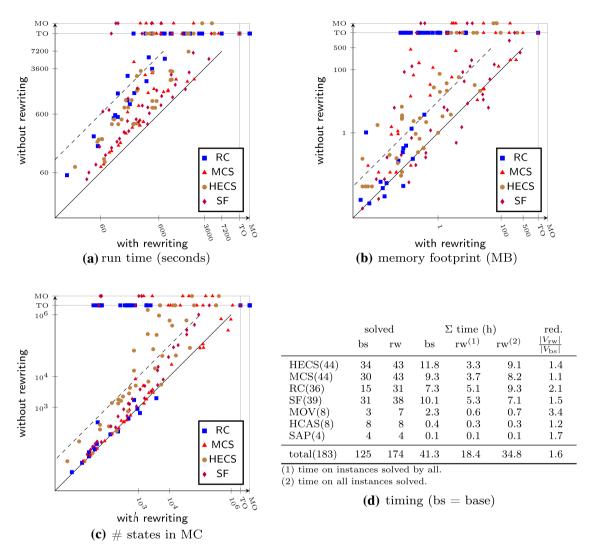

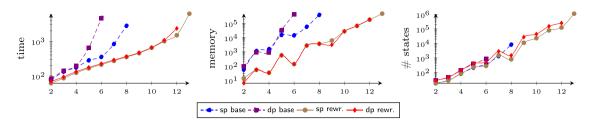

**Empirical evaluation.** We have implemented our rewrite technique by exploiting several existing tools. All our DFT rewrite rules are realised using the graph transformation tool GROOVE [GdMR<sup>+</sup>12]. Using the aforementioned heuristic, GROOVE takes an input DFT and rewrites it in a number of steps. The resulting DFT is analysed using the DFT analysis tool DFTCalc [ABvdB<sup>+</sup>13] which exploits the compositional state space generation and minimisation mentioned earlier. The analysis of the resulting CTMC is done with the model checker MRMC [KZH<sup>+</sup>11]. This together yields a fully automated tool chain for graph-based DFT reduction and analysis of common properties such as system reliability and availability. We have analysed several variations of seven benchmarks, comprised of over 170 DFTs in total, originating from standard examples from the literature as well as industrial case studies from aerospace and railway engineering. *Rewriting enabled to cope with 49 DFTs that could not be handled before*. For the other fault trees rewriting pays off, being much faster and more memory efficient, *up to two orders of magnitude*. This applies to both the peak memory footprint and the size of the resulting Markov chain (see Fig. 31b, c, page 48). This comes at no run-time penalty: graph rewriting is very fast and the CTMC generation is significantly accelerated due to the DFT reduction.

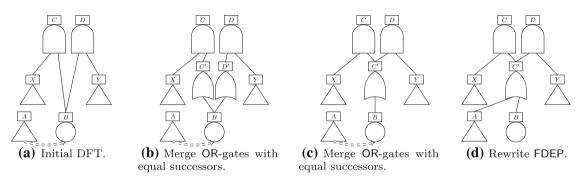

Fig. 2. Formalise DFT rewriting via standard graph transformation [EEPT06]

Summary of the main contributions. The major contributions of this paper are:

- A rewriting framework for DFTs that allows for simplifying DFTs prior to their state-space generation.

- 29 (families of) rewrite rules for DFT rewriting together with their correctness.

- A prototypical implementation using graph transformation techniques and tools.

- An extensive experimental evaluation showing the potential benefits and state-space reductions.

This paper extends our conference paper  $[JGK^+15]$  by a comprehensive presentation of all 29 (families of) rewriting rules, their correctness, and details about realising DFT rewriting as a standard graph transformation system. Full correctness proofs can be found in [Jun15].

**Related work.** Reduction of fault trees is a well-investigated topic. An important technique is to identify independent static sub-trees [PD96, LXL<sup>+</sup>10, HGH11, Yev11, RGD10]. These static sub-trees are analysed using efficient techniques (such as BDDs), whereas the dynamic parts require more complex methods. While such modular approaches yield significant speed ups, they largely depend on the DFT shape. Shared sub-trees, or a dynamic top-node, inhibits the application of these techniques. Merle et al. [MR07, MRLB10] map DFTs onto Boolean algebra extended with temporal operators. The resulting expressions can then be minimised via syntactic manipulation. This approach imposes several restrictions on the DFTs. Parametric fault trees [Rai05, BFGP03] exploit the symmetry in replicated sub-trees while translating DFTs (using graph transformation) to generalised stochastic Petri nets.

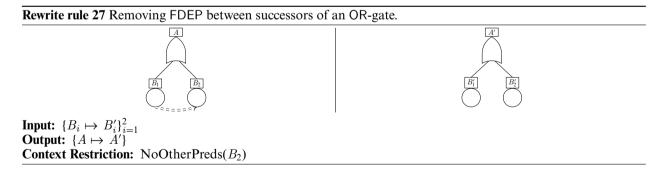

**Organisation of the paper.** Section 2 introduces DFTs, briefly describes their underlying CTMC, and provides several formal definitions relevant for the DFT rewriting. Section 3 introduces the main ingredients of graph rewriting. Section 4 explains the rewriting of DFTs such as context restrictions, DFTs as labelled graphs, what is a DFT rewrite rule, and well-formedness. Section 5 presents the 29 rewrite rules in detail and discusses their correctness. Section 6 describes how the DFT rewriting using graph transformation is realised in the graph transformation tool GROOVE. Section 7 presents the benchmark DFTs, provides the experimental results indicating the memory and time gains of DFT rewriting. Finally, Sect. 8 concludes the paper. Appendix A contains a table of often used notations. In Appendix B we briefly recap some formal definitions of graph rewriting.

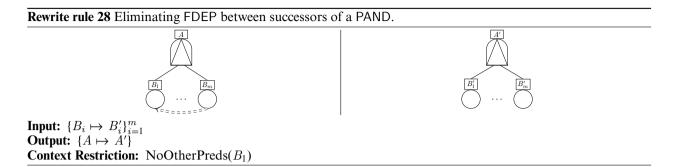

## 2. Dynamic fault trees

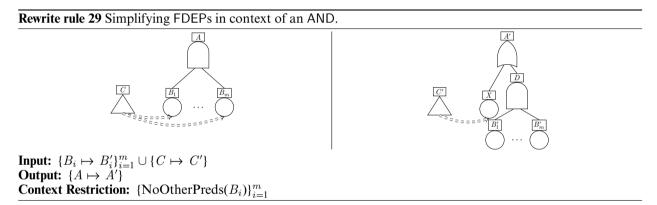

Fault trees (FTs,  $[SVD^+02]$ ) model how individual component failures propagate through a system and lead to system failures. Since subtrees can be shared, FTs are directed acyclic graphs (DAGs) rather than trees. The leaves of the tree (or rather, the sinks of the DAG) model basic component failure modes, and are called *basic events* (*BEs*). Fault tree *gates* model how component failures propagate and lead to system failures.

Fault trees on a diet

# 2.1. Static fault trees

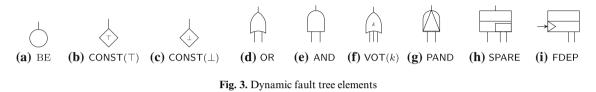

To model a component's failure behaviour, each BE is usually equipped with a *failure rate*  $\lambda$ , i.e., the parameter of an exponential probability distribution. The probability that the BE fails before time T is then given by  $1 - e^{-\lambda T}$ . Other probability distributions, like Weibull, are often supported as well. We call those BEs whose failure behaviour is governed probabilistically *event elements (EEs)*. Some BEs have already failed or never fail. Such BEs are called *constants*, and denoted by CONST( $\top$ ) and CONST( $\perp$ ) respectively. Fig. 3a–c depicts these BE types.

The non-sink nodes of the FT, i.e., nodes with one or more children (a.k.a. inputs of the node), are equipped with *gates*. Static fault trees (SFTs) feature three types of gates, depicted in Fig. 3d–f:

- The AND-gate fails if all its children fail;

- The OR-gate fails if at least one of its children fails;

- The VOT(m)-gate fails if at least m of its children fail.

Clearly, an OR-gate is equivalent to a VOT(1)-gate, and an AND-gate with m children to a VOT(m)-gate. Some SFT variants consider additional gates, like the XOR (exclusive OR) and the NOT-gate [SVD<sup>+</sup>02], which yield non-coherent behaviour and is only required in very special scenarios [CCR08].

A fault tree fails if its root, called the *top level event (TLE)*, fails. The TLE represents the failure condition of interest, such as the stranding of a train, or the unplanned unavailability of a data center, and is denoted by an underlined identifier. The failure of an SFT is determined by which BEs fail, and not by their order; hence their name *static*.

# 2.2. Dynamic fault trees

Static FTs appeal as a relatively simple, yet useful modelling tool. However, SFTs however cannot model several important failure patterns, such as: (a) *Order-dependent failures*, i.e. failures that only occur if BEs occur in a particular order. For example, a water leakage in a pump only leads to a short-circuit if the power supply has not failed before. (b) Simple support for *feedback loops*. Although systems with feedback loops in the error behaviour and cascaded errors can be modelled with SFTs, doing so requires verbose work-arounds which makes modelling error prone, cf. [SVD<sup>+</sup>02]. (c) *Spare management and spare parts*. A spare part is an interchangeable part that is used for the replacement of failed elements, e.g. spare car wheels. *Cold* spare parts can only fail while used. *Warm* spare parts can always fail but when being spare they fail with a reduced failure rate. *Hot* spare parts always have the same failure rate. SFTs can model hot spares via voting gates, but cold and warm spare cannot be represented.

To overcome these shortcoming *dynamic fault trees* (DFTs) were introduced, featuring three additional gates, see Fig. 3g-i:

- The (SPARE)-gate to model the management of spare parts;

- The priority-AND (PAND)-gate to model order dependent failures;

- The functional dependency (FDEP)-gate to model dependencies between failures and common cause failures.

These gates are called *dynamic*, since, unlike the static FTs, the order in which the BEs fail matters. Again, other dynamic gates exist, like the priority-OR, the sequence enforcer and the probabilistic dependency gate, see also [JGKS16]; we treat the most common ones here. Their behaviour is described below.

# 2.2.1. Basic events

An important property of spare management is that the failure behaviour of a spare depends whether or not it is in use. Components that are in use are called *active*; components not in use are *dormant* or *passive*. To accommodate this behaviour, DFTs do not only equip their BEs with a failure rate  $\lambda$ , as for SFTs, but also with a *dormancy factor*  $\alpha \in [0, 1]$ . The latter indicates how much the failure rate of a spare reduces when not in use: The probability for the BE to fail before time T is given by  $1 - e^{-\lambda T}$  when active, and by  $1 - e^{-\alpha \lambda T}$  when dormant. Thus, for a cold spare, we set  $\alpha = 0$ , so that it does not fail when dormant; a hot spare is given by  $\alpha = 1$ , so that it fails with the same rate no matter whether active or dormant; for a warm spare we set  $\alpha \in (0, 1)$ , so that it can fail when dormant, but with a lower rate  $\alpha \lambda$ .

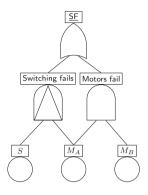

Fig. 4. Boom barrier example

As before, we label DFT leaves by the constant CONST(T) and  $CONST(\bot)$  to denote respectively that have already failed or never fail. Finally, leaves that only fail due to an FDEP are not labeled at all.

#### 2.2.2. Dynamic gates

The PAND-gate. A PAND-gate fails if its children fail from left to right; if the children fail in any other order, then the PAND-gate becomes *infallible*.

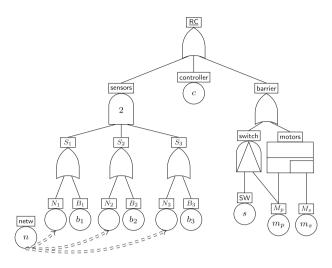

**Example 2.1** Figure 4 depicts a very typical usage of the PAND-gate to model the switching between two redundant components. This DFT models a the drive train of boom barrier. The system has two redundant motors ( $M_A$  and  $M_B$ ). A switch (S) connects either of the motors to the drive train; initially,  $M_A$  is connected to S. As soon as  $M_A$  fails, motor  $M_B$  can take over, but then the switch must first connect  $M_B$  to the barrier. This is only possible if the switch has not failed. Thus, the failure of the switch is only relevant if it occurs before  $M_A$  fails. The DFT reflects this behaviour as it only fails if either both motors fail, or if the switching fails, where the latter only happens if first the switch and then  $M_A$  fails.

Being DAGs rather than trees, one BE or gate may serve as input to several gates. Hence, it may happen that several children of a PAND-gate fail simultaneously. Different interpretations of the PAND-gate exist as to whether or not the PAND should fail in that case [JGKS16]. We assume it does so, i.e. we take the non-strict interpretation here. That is, the PAND fails if all its children have failed, and each *i*th child fails before or at the same time as the *i*+1th child.

**The SPARE-gate.** A SPARE-gate models the management of spare components. The first child of a SPARE-gate is called its *primary*, and is in use from the start. The other children are called *spares* or *spare children* and replace the primary when it fails.

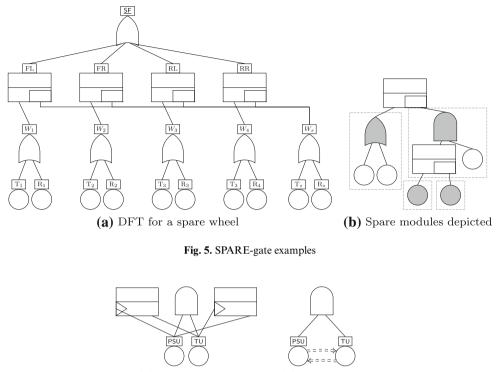

**Example 2.2** A typical example is a car with a spare wheel in the trunk, see Fig. 5a. The car contains four spots for wheels (denoted FL, FR, RL and RR front-left, front-right, rear-left, and rear-right). Initially, wheels  $W_1$  to  $W_4$  are mounted, while the spare wheel  $W_s$  is in the trunk. Each wheel fails due to either a tire-fault ( $T_i$ ) or a rim-fault ( $R_i$ ). If (say)  $W_3$  fails, then it is replaced by the spare wheel  $W_s$ . If any further wheel fails, then no spare wheel is left to replace  $W_3$ , so the system fails.

If an (either primary or spare) child of a SPARE-gate fails, then the SPARE-gate attempts to switch to the next (from left to right) available spare, i.e., a child that has not yet failed, and that is not in use by any other SPARE-gate. The process of obtaining the next available spare is called *claiming*. If a SPARE-gate has no available spare anymore, it fails.

In order to describe activation, we group elements in so-called *(spare-)modules*. Modules are subgraphs represented by a child of a SPARE-gate. In Fig. 5, we have in grey the representative of the sets of elements indicated by dotted boxes. In a module, all elements have the same activation status, and they are all activated at once. The precise extent of the modules is described in Sect. 2.4.4. We also construct a top module, represented by the TLE. Initially, the top module is active, furthermore, for each active SPARE-gate also the module represented by its used child is active. All BEs in an active module fail according to their active failure rate, all others fail according to their dormant failure rate.

#### Fault trees on a diet

(a) Gate notation (b) Arrow notation

Fig. 6. A feedback loop using two notations for FDEPs

**The** FDEP **gate**. The FDEP gate causes other elements to fail. The leftmost child is called a *trigger*, the other children are called *dependent events*. The behaviour of the FDEP is that, if the trigger fails, all dependent events automatically fail. In this way, FDEPs are used to represent common cause failures and feedback loops, such as a fire that causes all equipment at a particular location to fail.

**Example 2.3** The DFT in Fig. 6a shows a feedback loop between a power supply unit (PSU) and a thermal unit (TU), modelling their mutually dependent failure: a failure of the PSU is leads to the failure of the TU, and vice versa.

By introducing FDEPs we now have two ways of passing failures between elements:

- 1. Failure propagation from an element to its parents (as in SFTs), or

- 2. Failure forwarding from an element to an EE (by FDEPs).

We assume that failure propagation takes presence over failure forwarding. That is, first we take into account the results of failure propagation, and only then consider if there is an opportunity for failure forwarding to let a dependent event fail: if so, we again first do the failure propagation. Put it differently, we only forward failures if no gate can fail anymore.

The presence of FDEPs yields two reasons for EEs to fail:

- 1. (Internal) failure forwarding an EE is triggered by an FDEP and has not failed before, or

- 2. External failure causes an EE fails due to a basic event and has not failed before.

Failure forwarding is ordered, but non-deterministic. That is, if one trigger is connected (via multiple FDEPs) to multiple dependent events, then the order in which the dependent events fail is not specified, i.e., any order can occur. If these dependent events are connected by a PAND-gate, then choosing a particular failure order influences whether or not the TLE fails, and therefore the quantitative measures, like the reliability. One can, however, study best-case versus worse-case scenarios, see Sect. 2.3.2.

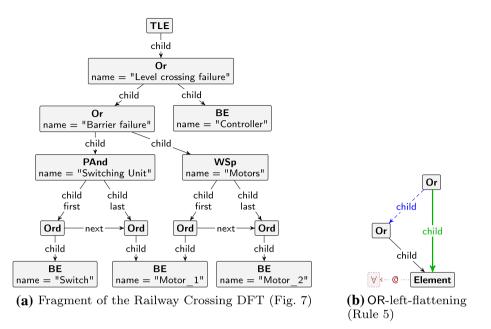

Fig. 7. Variant of the railway crossing DFT

By connecting the same trigger to multiple FDEP-gates, we can assume w.l.o.g. we that all FDEPs are binary, i.e. contain a single dependent event. To simplify the figures, we depict FDEPs by double-dotted arrow from the trigger to the dependent event, rather than by a (more explicit) gate; see Fig. 6a versus b.

**Example 2.4** The DFT in Fig. 7 represents a simplified railway level crossing [GKS<sup>+</sup>14]. The system consists of three sensors, barriers as in Fig. 4, and a controller and fails if either of these subsystems fails. The sensor system fails if at least two of the three redundant sensors  $(S_1, S_2, S_3)$  fail. Sensor  $S_i$  fails either due to their battery  $(B_i)$  or due to a failed network cable  $(N_i)$ . Furthermore, a network problem (netw) causes all sensor network connections  $N_i$  to fail, as modelled by the three FDEP-gates. Finally, the barrier fails if either the main and spare motor fail, modelled by the SPARE-gate Motors, or if the switch and then a motor fails, as modelled by the PAND-gate.

As basic events, we consider failures of the network (n), the batteries  $(b_1, b_2, b_3)$ , the controller (c), the switch (s), or the motors  $(m_p, m_s)$ . We attach these basic events to the corresponding EEs, indicated by placing the basic events inside the circles.

We do not consider basic events for the network failure of the sensors. The only way that the EEs  $N_1$ ,  $N_2$ , and  $N_3$  can fail is thus internally.

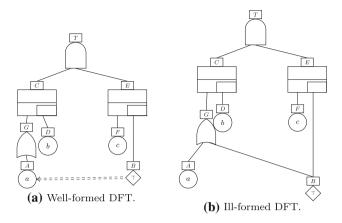

#### 2.2.3. Well-formedness

In order to be meaningful, DFTs must adhere to some well-formedness conditions:

- 1. The DFT is acyclic;

- 2. VOT(k)-gates have at least k children;

- 3. The TLE is not an FDEP;

- 4. FDEPs have no parents;

- 5. All dependent events of an FDEP are event elements;

- 6. Spare modules, i.e., sub-trees under a SPARE-gate, are independent;

- 7. Primary spare module representatives, i.e., first children of a SPARE-gate, do not contain any CONST(T) elements; and

- 8. Primary spare modules are not shared over multiple SPARE-gates.

The conditions (1-5) are standard and self-explanatory. The independence of two spare modules (6) prevents ambiguity in the meaning of claiming spares. Constraint (7) enables us to simplify the definition of the initially claimed elements. Constraint (8) again simplifies matters: primary modules are initially claimed by a unique SPARE-gate, and therefore they cannot be claimed later on and sharing them is superfluous.

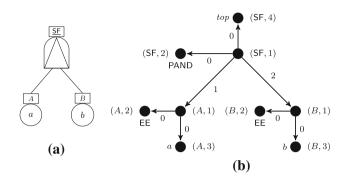

Fig. 8. Three simple DFTs and their state-transition semantics

## 2.3. DFT analysis

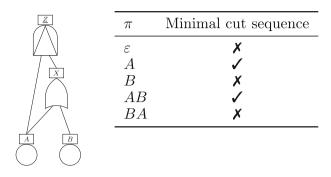

#### 2.3.1. The state space of a DFT

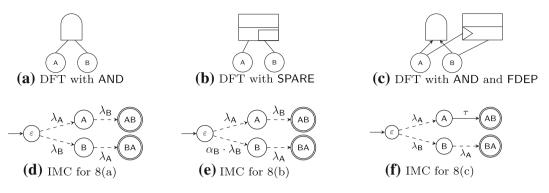

The semantics of a DFT F is—like in [CSD00]—expressed using a state-transition system  $C_F$ , where transitions correspond to the failure of an EE and states to sequences of distinct EEs. As our interest is in quantitative analysis of DFTs, transitions are labeled with the failure rate of an EE. The triggering of events using FDEPs (internal failures) is instantaneous and is instead modelled by a transition that is labelled by an action (denoted  $\tau$ ). The resulting state-transition system  $C_F$  thus has two types of transitions: rate-labeled and  $\tau$ -labelled transitions. This is known as an interactive Markov chain (IMC, for short) [Her02]. The detailed construction of  $C_F$  is given in Sect. 2.4. Here, we illustrate the DFT semantics by three small examples, see Fig. 8. For ease of reference, we labelled each state with the sequence of failed EEs. The DFT in Fig. 8a fails if EE A fails before B, or B and A fail in the reverse order, see Fig. 8d. The DFT in Fig. 8b fails if EEs A and B fail, as above. However, if A has not yet failed, then the failure rate of B is reduced by the dormancy factor  $\alpha_B$ . Thus, B is initially dormant, and fails with rate  $\lambda_B \cdot \alpha_B$  (see Fig. 8e). The DFT in Fig. 8c also fails if EEs A and B fail. However, the failure of A causes B to fail immediately afterwards, as realised by the  $\tau$ -transition in Fig. 8f.

#### 2.3.2. DFT measures

We define the quantitative measures on a DFT F in terms of the IMC  $C_F$ . Let Fail be the set of states in IMC  $C_F$  in which the *top* event in F has failed. Recall that, if one FDEPs trigger triggers several dependent events, their order is non-deterministically resolved. This is formalised using a scheduler (or policy) S on  $C_F$ , resulting in a continuous-time Markov chain  $C_F[S]$ .

**Definition 2.1** (*Quantitative* DFT *measures*) Let F be a DFT, S a scheduler on F and  $t \in \mathbb{R}$ .

- $\mathsf{RELY}_{F[S]}^t = \Pr_{\mathcal{C}_F[S]}(\Diamond^{\leq t} \mathsf{Fail})$  is the reliability of F under S given mission time t.

- $\mathsf{MTTF}_{F[S]} = \mathsf{ET}_{\mathcal{C}_F[S]}(\Diamond \mathsf{Fail})$  is the mean time to failure in F under S.

We define the *reliability of* F given mission time t as tuple  $\mathsf{RELY}_F^t = (\min_{\mathcal{S}} \mathsf{RELY}_{F[\mathcal{S}]}^t, \max_{\mathcal{S}} \mathsf{RELY}_{F[\mathcal{S}]}^t)$  and the mean time to failure in F as tuple  $\mathsf{MTTF}_F = (\min_{\mathcal{S}} \mathsf{MTTF}_{F[\mathcal{S}]}, \max_{\mathcal{S}} \mathsf{MTTF}_{F[\mathcal{S}]})$

Here,  $Pr(\Diamond^{\leq t} Fail)$  stands for the probability of all paths that reach a state in Fail ultimately at time t, whereas  $ET(\Diamond Fail)$  stands for the expected time until reaching a state in which the top element of the DFT has failed. These notions can be defined on the IMC in a standard way and go beyond the scope of this paper. For more information, we refer to [GHH<sup>+</sup>14].

We focus on quantitative measures as their analysis is typically most time consuming. The rewriting of many other quantitative measures can also be defined on the IMC. Most rewriting rules are shown to preserve the IMC up to isomorphism—which is also the correctness argument used (cf. Sect. 5.4) for these rules, therefore, using only the adequate subset of rules preserves most quantitative measures. Regarding qualitative measures, one can similarly use a subset of rules which preserve the property at hand. Example measures for the DFT in Fig. 7 are: "what is the reliability of the level crossing for a time frame of 10 years after deployment?" (reliability), or "what is the mean time until a first failure of the level crossing occurs?" (MTTF).

## 2.4. Formal definitions

## 2.4.1. DFT syntax

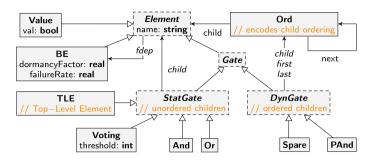

To formally describe DFTs, we assume a fixed set BasicEvents containing all basic events, which are assigned a failure rate and dormancy factor via the function  $\Lambda$

$\Lambda$  : BasicEvents  $\rightarrow \mathbb{R}_{>0} \times [0, 1]$

DFT nodes are referred to as *elements*. They are partitioned into *leaves* and gates.

Leaves = {EE, CONST( $\top$ ), CONST( $\perp$ )} Gates = {AND, OR, PAND, FDEP, SPARE}  $\cup$  {VOT(k) |  $k \in \mathbb{N}$ }

Recall that event elements (EEs) fail according to a probability distribution,  $CONST(\perp)$  leaves never fail and  $CONST(\top)$  leaves have failed already.

**Definition 2.2** (*Dynamic fault tree*) Formally, a DFT F is a tuple  $(V, \sigma, Tp, \Theta, top)$ , where

- V is a finite set of *nodes*.

- $\sigma: V \to V^*$  maps each node to its (ordered) successors, also called *children* or *inputs*.

- $Tp: V \to \text{Gates} \cup \text{Leaves}$  is a *typing*, mapping leaf nodes  $(v \in V \text{ with } \sigma(v) = \epsilon)$  to Leaves and other nodes to Gates. For  $K \in \text{Gates} \cup \text{Leaves}$ , let  $F_K = \{v \in V \mid Tp(v) = K\}$  be the nodes of type K.

- $\Theta: F_{\mathsf{EE}} \twoheadrightarrow \mathsf{BasicEvents}$  is the (partial) injective *attachment* function.

- $top \in V$  is the unique top element.

We often write "v is a K" for  $v \in F_K$ . The attachment function  $\Theta$  is partial, i.e., some event elements have no associated **BasicEvents**, allowing a more modular simplification of the FDEP in Sect. 5.3. For node v of a DFT with children  $\sigma(v) = v_1 \cdots v_n$ , let  $\sigma(v)_i = v_i$  denote the *i*th input of v, child $(v) = \{v_1, \ldots, v_n\}$  the set (rather than the sequence) of all inputs, and parent $(v) = \{v' \mid v \in \text{child}(v')\}$  the set of v's predecessors.

**Example 2.5** The DFT in Fig. 7 is formally given as  $(V, \sigma, Tp, \Theta, top)$  with

- $V = \{\text{RC}, \text{sensors}, \text{controller}, \text{barrier}, \text{switch}, \text{motors}, \text{SW}, M_p, M_s, S_1, S_2, S_3, \dots, X_1, X_2, X_3\}$  where  $X_i$  denote the FDEPs.

- $\sigma$  given by sensors  $\mapsto S_1, S_2, S_3; S_1 \mapsto N_1, B_1; N_1 \mapsto \varepsilon; X_1 \mapsto \mathsf{netw}, N_1; S_2 \mapsto N_2, B_2; N_2 \mapsto \varepsilon; \ldots;$  where  $\varepsilon$  denotes the absence of successors.

- Tp given by sensors  $\mapsto$  VOT(2);  $S_i \mapsto$  OR,  $N_i \mapsto$  EE,  $B_i \mapsto$  EE for all  $i \in \{1, \ldots, 3\}$ ;  $X_1 \mapsto$  FDEP;  $X_2 \mapsto$  FDEP; ....

- $\Theta$  given by netw  $\mapsto n$ ;  $B_1 \mapsto b_1$ ;  $B_2 \mapsto b_2$ ;  $B_3 \mapsto b_3$ ; SW  $\mapsto s$ ; ... and undefined on  $N_1, N_2, N_3$ .

- $top = \mathsf{RC}$ .

#### 2.4.2. The graph underlying a DFT

Each DFT F induces an underlying graph  $G_F$  whose edges point from a node to its children. That is, (v, v') is an edge if v' is a child of v. Thus, paths in  $G_F$  "walk down the tree," going from higher to lower nodes in F. The undirected graph  $G_F^{i=}$  contains edges from parent to child and from child to parent.

**Definition 2.3** (Underlying graph of a DFT) The simple graph of DFT  $F = (V, \sigma, Tp, \Theta, top)$  is  $G_F = (V, E)$ where  $E = \{(v, v') \in V \times V \mid v' \in \text{child}(v)\}$ . Let  $G_F^{\subseteq} = (V, E \cup E^{-1})$  be the undirected graph of DFT F.

A sequence  $v_0 e_1 v_1 \dots e_n v_n \in V \times (E \times V)^n$  is a *path from*  $v_0$  to  $v_n$  through a graph G = (V, E) if  $e_{i+1} = (v_i, v_{i+1})$  for all  $0 \le i < n$ . The set Path<sub>F</sub>(x, y) denotes all paths from x to y through  $G_F^{\le i}$ .

Fault trees on a diet

We define the set of descendants dec(v) of a node  $v \in V$  as all nodes v' that can be reached from v via a path in the underlying graph  $G_F$ . The set of ancestors anc(v) contains all nodes v' from wich v can be reached in  $G_F$ .

$dec(v) = \{v' \in V \mid \text{ there exists a path from } v \text{ to } v' \neq v \text{ in } G_F\}$  and  $anc(v) = \{v' \in V \mid \text{ there exists a path from } v' \neq v \text{ to } v \text{ in } G_F\}.$

Example 2.6 Consider the DFT in Fig. 7. We have

- child(sensors) =  $\{S_3, S_1, S_2\}$  (that is, an unordered set),

- parent( $M_p$ ) = {switch, motors},

- dec(sensors) =  $\bigcup_{1 \le i \le 3} \{S_i, B_i, N_i\},\$

- $\operatorname{anc}(M_p) = \{ \operatorname{switch}, \operatorname{motors}, \operatorname{barrier}, \operatorname{RC} \}.$

#### 2.4.3. State of a DFT

We use the following notations. Let  $\mathcal{P}(A)$  denote the powerset of a set A and  $\mathcal{P}_k(A)$  denote all subsets of A of cardinality k. We use  $K^*$  to denote the set of (finite) words over alphabet K where  $\varepsilon$  denotes the empty word and  $K^{\triangleright}$  are the words over K without repetition.

As described in Sect. 2.3.1, the state of DFT F depends on the events that have failed and their ordering. We use  $F_{EE}^{\triangleright} \subseteq F_{EE}^{*}$  to denote the set of ordered sequences of event element failures and  $\pi$  for elements in  $F_{EE}^{\triangleright}$ . Then the state of the DFT F after the subsequent occurrence of the events in  $\pi$  is characterised by two predicates, Failed( $\pi$ ) and ClaimedBy( $\pi$ ). The first predicate describes which elements are considered failed after  $\pi$  occurred, the second maps spare module representatives to SPARE-gates that claimed them. The DFT semantics guarantees that each spare module is claimed by at most one SPARE-gate.

To define these predicates, we use a set of relations. For DFT  $F = (V, \sigma, Tp, \Theta, top)$  let  $\models_F \subseteq V \times F_{\mathsf{EE}}^{\triangleright}$  be the *model-relation*, and  $\dagger_F^s \subseteq V \times F_{\mathsf{EE}}^{\triangleright}$  be the *claiming-relation* for SPARE-gate *s* in *F*. The model-relation describes whether a node  $v \in V$  fails for a given event trace  $\pi \in F_{\mathsf{EE}}^{\triangleright}$ , and the claiming-relation describes whether a node  $v \in V$  is claimed by a spare for a given event trace  $\pi \in F_{\mathsf{EE}}^{\triangleright}$ .

**Definition 2.4** (*Failed events after a trace*) Let  $F = (V, \sigma, Tp, \Theta, top)$  be a DFT and  $\pi \in F_{\mathsf{EE}}^{\triangleright}$ . The set of failed elements after  $\pi$  is defined as

Failed:  $F_{\mathsf{EE}}^{\triangleright} \to \mathcal{P}(V)$ , Failed $(\pi) = \{ v \in V \mid v \models_F \pi \}$ ,

and the mapping of *representatives claimed by after*  $\pi$  as

ClaimedBy:  $F_{\mathsf{EE}}^{\triangleright} \to (V \to \mathcal{P}(F_{\mathsf{SPARE}}))$ , ClaimedBy $(\pi)(v) = \{s \in F_{\mathsf{SPARE}} \mid v_F^* \pi\}$ .

**Example 2.7** Consider the DFT in Fig. 7. Let  $\pi = \langle SW, M_p \rangle$  and  $\pi' = \langle M_p, SW \rangle$ . Then Failed $(\pi) = \{SW, switch, barrier, RC\}$ , whereas Failed $(\pi') = \emptyset$ . The difference in the traces  $\pi$  and  $\pi'$  is the order of failed EEs. For switch  $\in F_{PAND}$ , the model relation asserts that the node fails if all children fail in order. Thus, switch  $\models_F \pi$  but switch  $\nvDash_F \pi'$ . The claiming-relation is only interesting for the spares, where ClaimedBy $(\cdot)(M_p) = \{Motors\}$  for  $\pi$  and  $\pi'$ .

#### 2.4.4. FDEPs, modules and activation

**Functional dependencies.** Once a trigger event fails, the FDEP-gate causes the dependent event element to fail. The direct relation of functional dependencies by dependent events is defined as:

$DepEvents(v) = \{\sigma(w)_i, i > 1 \mid w \in \mathsf{FDEP}, \sigma(w)_1 = v\}.$

The set of *dependent* or *triggered events* of trace  $\pi$  is given by:

$DepEvents(\pi) = \{ w \notin \pi \mid v \in Failed(\pi) \text{ and } w \in DepEvents(v) \}.$

States with  $\text{DepEvents}(\pi) \neq \emptyset$  only have outgoing  $\tau$ -transitions.

**Example 2.8** Consider the DFT in Fig. 7. We have DepEvents(netw) =  $\{N_1, N_2, N_3\}$  and DepEvents $(N_1) = \emptyset$ . Furthermore, for  $\pi = \langle N_1 \rangle$ , DepEvents $(\pi) = \emptyset$  and for  $\pi = \langle N_1, \text{netw} \rangle$  we have DepEvents $(\pi) = \{N_2, N_3\}$ .

**Spare modules.** Spare modules are sets of elements that are claimed and activated together. Each module is represented by a representative r, which is a child of a SPARE-gate. As functional dependencies are not supposed to propagate activation, elements which are only connected via functional dependencies are separate modules. Furthermore, children of a spare are usually another spare module, thus the paths connecting SPARE-gates to their children should not define a connection of elements. Modules consist of sets of elements which are connected via *module paths*.

**Definition 2.5** (*Module path*) A path  $p = v_0 e_1 v_1 \dots e_n v_n$  in  $G_F^{\leq i}$  of DFT  $F = (V, \sigma, Tp, \Theta, top)$  is a module path from  $v_0$  to  $v_n$  if the following conditions hold

- $v_i \notin V_{\text{FDEP}}$ , for all  $0 \le i \le n$ ,

- $v_i \in V_{\text{SPARE}} \Rightarrow v_{i+1} \in \text{parent}(v_i)$ , for all  $0 \le i < n$ ,

- $v_i \in V_{\text{SPARE}} \Rightarrow v_{i-1} \in \text{parent}(v_i) \text{ for all } 1 \le i \le n.$

The set of module paths from  $v \in V$  to  $v' \in V$  is denoted by  $ModPath_F(v, v')$ .

Modules are represented by the children of SPAREs or by the *top* element—every element connected via a module path to a representative is in the same module: Let the set of *module representatives* be defined as  $(\bigcup_{s \in F_{SPARE}} \text{child}(s)) \cup \{top\}$ . Given a module representative r, the *module represented by* r is defined as  $\text{Mod}_r = \{v \in V \mid \text{ModPath}_F(r, v) \neq \emptyset\}$ . If r = top, the corresponding module is called the *top module*, otherwise it is called a *spare module*. We drop the subscript F whenever it is clear from the context. For every spare gate s, we call  $\sigma(s)_1$  the *primary spare module representative* and the spare module it represents a *primary module*.

**Example 2.9** Consider the DFT in Fig. 5a. Each set  $\{W_i, T_i, R_i\}$ , for i = 1, 2, 3, 4, s, is a module with representative  $W_i$ . Sets  $W_1$ ,  $W_2$ ,  $W_3$  and  $W_4$  are primary modules. The top module {SF, FL, FR, RL, RR} is represented by SF.

*Remark* 1 Some models do not have strictly separated spare modules; which is unproblematic due to the following observation (formally discussed in [BCS10]): Any element connected via a module path to the root element is initially activated. Likewise, elements connected to the primary children of non-nested SPARE-gates are initially activated. Thus, the notion of modules is not necessary for primary activated modules. As an example, consider the DFT depicted in Fig. 7, where  $m_p$  is both connected to a top and (trivially) to the primary child of the SPARE-gate. For simplicity, we do not formally allow this construction here as it overcomplicates the definitions. Notice that this does not have any impact, as (i) the construction are simply syntactic sugar and (ii) such occurrences can be easily detected.

Activation. The module represented by *top* is always active. Basic events are activated whenever they are attached to event elements which are part of an active module. Modules are activated when their representative is claimed by an active spare, or the spare which claimed their representative becomes active. To describe which event elements are active, let Active be defined as the least fix-point such that:

Active:

$$F_{\mathsf{EE}}^{\rhd} \to \mathcal{P}(V)$$

,

Active( $\pi$ ) = Mod<sub>top</sub>  $\cup \bigcup \{ Mod_r \mid ClaimedBy(\pi)(r) \subseteq Active(\pi) \}.$

A basic event is *activated* whenever its corresponding EE is active:

Activated( $\pi$ ) = { $\omega \in \text{BasicEvents} \mid \exists v \in F_{\text{EE}} \Theta(v) = \omega \land v \in \text{Active}(\pi)$ }.

**Example 2.10** Consider the DFT in Fig. 7. We have Active( $\varepsilon$ ) =  $V \setminus \{\text{netw}, M_s\}$ . For  $\pi = \langle M_p \rangle$  we get Active( $\pi$ ) =  $V \setminus \{\text{netw}\}$ . We get Activated( $\varepsilon$ ) =  $\{b_1, b_2, b_3, s, c, m_p\}$  and Activated( $\pi$ ) = Activated( $\varepsilon$ )  $\cup \{m_s\}$ .

# 3. Graph rewriting

The previous section has provided preliminaries and formal definitions of DFTs and related concepts. This section focuses on the second main ingredient of this paper: graph rewriting. As we exploit well-known results from graph

Fig. 9. Example for DPO graph rewriting [EEPT06]

rewriting, we give a brief introduction into graph rewriting and fix some notations. More detailed accounts on graph rewriting can be found in [EEPT06, Hec06]. We ensured that the essential results of this paper can be followed without a deeper understanding of graph rewriting theory.

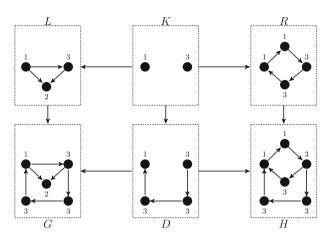

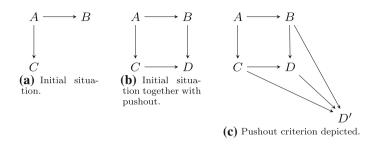

We use the algebraic approach which has its roots in category theory. Multiple variants for this algebraic approach exist. We choose the double pushout (DPO) approach, as introduced by Ehrig et al. in [EPS73]. Essentially, a *rule* consists of two graphs, L and R, with a common *interface* K, which can roughly be thought of as a subgraph of both L and R—with a caveat discussed after the example below. *Rewriting* of a host graph G using the rule is done by finding a subgraph in G which matches L; this boils down to finding a mapping from L to that subgraph. G is then rewritten by (roughly) removing the image of  $L \setminus K$  and adding an image of  $R \setminus K$ . Before giving a formal definition, we illustrate rewriting by an example from [EEPT06].

**Example 3.1** We describe the application of a given rewrite rule on a given host graph. All graphs have vertex labels taken from  $\{1, 2, 3\}$  and edge labels  $\{x\}$ . Figure 9 depicts the rule (graphs L, K, R) which is applied to the host-graph (G). We give an intermediate step (D) and the final result (H). We omit any edge labels in the figure. The arrows between the graphs depict the graph morphisms and are explained below.

Graph L describes the subgraph which has to be matched in a host graph. The graph K describes a subgraph of L referred to as the *interface*. After successfully matching L in G, elements which are matched by L but not by K are removed, yielding graph D. D has to be a valid graph, so dangling edges (i.e., edges without a source or target vertex) are not allowed. To prevent dangling edges in D, additional conditions are imposed on the match of L in G. In this particular example, we trivially match L in G, after which we remove all matched edges and the vertex labelled 2. This yields D.

To finalise the rewriting step, graphs R and D are merged, such that elements which originate from the interface K are not duplicated. In this particular example, we add graph R to graph D, merging the images (in R and D) of the two vertices from K are merged, yielding H.

In the example, the mapping from K to R is injective, and thus K is essentially a subgraph of R. However, in general, the relation is given by a possibly non-injective morphism. A non-injective morphism intuitively means that some nodes in D have to be merged to obtain H. Thus, if the morphism is non-injective, the second step, in addition to gluing R to D, also merges any nodes of D that are images of K-nodes with a common image in R. In other words, if nodes of K are mapped non-injectively into R, this induces a node merge in the rewrite step.

We apply graph rewriting on *labelled graphs*, digraphs whose vertices and edges are labelled. Let  $\Sigma = \Sigma_v \uplus \Sigma_e$ be a (globally given) *label universe* consisting of disjoint sets of *vertex labels*  $\Sigma_v$  and *edge labels*  $\Sigma_e$ .

**Definition 3.1** (*Labelled graph, graph morphism*) A *labelled graph* G = (V, E, src, tar, lab) where

- V and E are disjoint finite sets of vertices V and edges E;

- src, tar:  $E \rightarrow V$  are functions defining the *source* and *target* vertices, respectively;

- $\mathsf{lab} = \mathsf{lab}_v \uplus \mathsf{lab}_e$  is the *labelling*, with *vertex-labelling*  $\mathsf{lab}_v \colon V \to \Sigma_v$  and *edge-labelling*  $\mathsf{lab}_e \colon E \to \Sigma_e$ .

Given two labelled graphs G and H, a graph morphism  $m : G \to H$  is a function  $m : (V_G \uplus E_G) \to (V_H \uplus E_H)$ that can be decomposed as  $m = m_v \uplus m_e$  with label mapping  $m_v : V_G \to V_H$  and edge mapping  $m_e : E_G \to E_H$ , which preserves edge sources, targets and labels: i.e., such that  $m_v \circ \operatorname{src}_G = \operatorname{src}_H \circ m_e$ ,  $m_v \circ \operatorname{tar}_G = \operatorname{tar}_H \circ m_e$ and  $\operatorname{lab}_G = \operatorname{lab}_H \circ m$ .

When this does not give rise to any confusion, we sometimes write "a morphism  $G \twoheadrightarrow H$ " without referring to the name of the morphism. Let In, Out:  $V \rightarrow \mathcal{P}(E)$  denote the set of incoming and outgoing edges of a given node, respectively, and InV, OutV:  $V \rightarrow \mathcal{P}(V)$  denote their source (target) vertices. These notations are used in Sect. 4.4.

In:  $v \mapsto \{e \in E \mid \mathsf{tar}(e) = v\}$  Out:  $v \mapsto \{e \in E \mid \mathsf{src}(e) = v\}$ InV:  $v \mapsto \{\mathsf{src}(e) \mid e \in \mathsf{In}(v)\}$  OutV:  $v \mapsto \{\mathsf{tar}(e) \mid e \in \mathsf{Out}(v)\}$ .

A rewrite rule (the upper part in Fig. 9) is formalised as follows.

**Definition 3.2** (*Graph rewrite rule*) A graph rewrite rule is a tuple  $r = (L, K, R, K \rightarrow L, K \rightarrow R)$  with

- L, K, R are labelled graphs

- $K \rightarrow L, K \rightarrow R$  are morphisms, with  $K \rightarrow L$  injective.

We call *L* the *left-hand side*, *R* the *right-hand side* and *K* the *interface* of rewrite rule *r*. We often abbreviate a rule by  $(L \leftarrow K \rightarrow R)$ . A rule is injective if  $K \rightarrow R$  is injective.

For the purpose of this paper, it is important to realise that applying a graph rewrite rule r to a graph G consists of two steps:

1. Finding a match m of L, the rule's left-hand side graph, into G. Such a match is actually given by a graph morphism that satisfies the following two conditions (besides being a morphism):

No dangling edges For all  $e \in E_G$  and all  $v \in V_L$  not in the image of  $K \rightarrow L$ , if  $m(v) = \operatorname{src}(e)$  or  $m(v) = \operatorname{tar}(e)$  then e = m(e') for some  $e' \in E_L$ .

No confusion for deleted elements For all  $x \in V_L \uplus E_L$  not in the image of  $K \twoheadrightarrow L$ , there is no  $y \in (V_L \uplus E_L) \setminus \{x\}$  such that m(x) = m(y).

There may be more than one appropriate morphism between any two graphs, or none; so the step of finding a match is both non-deterministic and uncertain to succeed.

2. Building a new graph by deleting, creating and merging elements as dictated by the remainder of the rule. Given a match, this step is completely deterministic (up to the choice of the identity of fresh target nodes and edges, which choice however does not affect the structure of the target graph).

The formal definition of rule application (step 2 above) can be found in Appendix B.

## 4. A framework for rewriting dynamic fault trees

DFTs tend to be verbose. They are often based on the system architecture, therefore reflecting the sub-system structure [SVD<sup>+</sup>02]. Modern techniques automatically generate DFTs from architectural description languages [BCK<sup>+</sup>11], yielding rather verbose DFTs too. As state-of-the-art DFT analysis algorithms typically construct an underlying state space that is exponential in the size of the input DFT, it is a natural idea to shrink DFTs prior to their analysis. We do so by *rewriting* of DFTs.

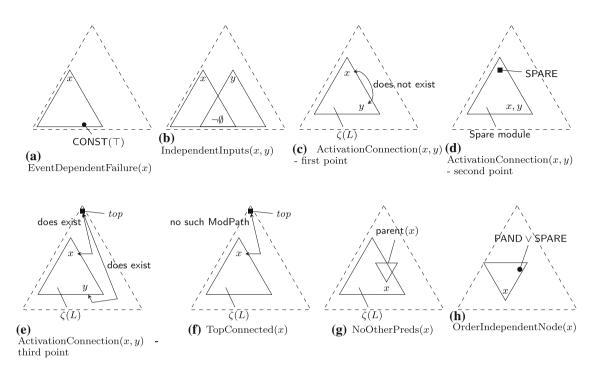

This section describes in detail what it means to rewrite (well-formed) DFTs. We start off in Sect. 4.1 by showing that DFT rewriting is not context-free. Section 4.2 describes how to encode all information of a DFT in a labelled graph; this provides the basis for reducing DFT rewriting to graph rewriting. Section 4.3 then describes what a rewrite rule for DFTs is. Section 4.4 defines the semantics of a DFT rewrite rule. Finally, Sect. 4.5 discusses how to ensure that the result of DFT rewriting is well-formed. At the end of this section, we have all concepts in place to rewrite a (well-formed) DFT into another (well-formed) DFT. The formal relationship between these DFTs is discussed later in Sect. 5.

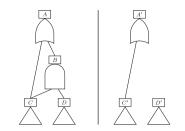

Fig. 10. The correctness of DFT rewriting depends on the context. Rewriting (a) into (b) is valid, while rewriting (c) into (d) is not, see Example 4.1

### 4.1. The need for context conditions

Simplifying *static* fault trees (SFTs) can be done by Boolean manipulations [SVD<sup>+</sup>02]. This remains true in the presence of FDEPs, but no longer holds for DFTs with dynamic gates such as SPAREs and PANDs, for which context-dependent rules are required.

**Example 4.1** In the DFT in Fig. 10a, gate A fails if and only if C fails. It may seem a general rule that the OR-gate B does not contribute to the failure behaviour of A and can therefore be removed as a successor of A, as depicted in Fig. 10b. If, however, we apply the same reasoning in Fig. 10c, then we obtain an invalid result: by removing the path from A to D, we prevent the activation of D; in the DFT Fig. 10d, D is never activated. In particular, if D is in cold standby, then D never fails in Fig. 10d, and thus never triggers C, which leads to a higher reliability and MTTF than for the DFT in Fig. 10c. Since the our rewrite rules aim to preserve the reliability and MTTF, we disallow rewriting Fig. 10c to d.

#### 4.2. Encoding DFTs as labelled graphs

In order to encode DFTs as graphs, we first consider the representation of DFT gates as graph vertices. DFTs are akin to labelled graphs, with one important difference: children of DFT gates are ordered. We use edge labels to encode this order in the graph encoding of a DFT. Furthermore, we cannot label vertices with the node type directly: untyped nodes in the left-hand side of the rule should match any (arbitrarily typed) node; yet matching nodes requires the same labels. Hence, we introduce an auxiliary vertex which carries the type information. Thus, the graph encoding of a DFT contains two to four vertices for each DFT node v: element vertex (v, 1) corresponds to v; carry vertex (v, 2) carries the type information for v; and, event element vertex (v, 3) encodes the attachment  $\Theta$ . The DFT gate *top* has an extra vertex (v, 4). Graph vertices are labelled as follows: element vertices are labelled with the basic events as given by  $\Theta$ .

The edges of the DFT encoding are defined as follows: as element vertices encode the DFT structure, there is an edge from (v, 1) to (v', 1) if v is a parent of v' in the DFT. There is also an edge between the carry vertex and (for EEs with an attached basic event) basic event vertices to the element vertices with edges from (v, 1) to (v, 2)and (if applicable) from (v, 1) to (v, 3). The edge labels are used to encode the order of the children. That is, the edge from (v, 1) to (v', 1) is labelled by an order-preserving mapping, defined below. All other edges, i.e. all edges to carry- and basic element vertices, are labelled by a—meaningless—number 0.

**Example 4.2** Figure 11 depicts a DFT and its encoding as labelled graph. The encoding has three element vertices, with on their left side their carry vertices. Moreover, the topmost vertex has a carry vertex which identifies it as the top vertex, while the two basic elements have extra carry vertices for the attachment function. All carry vertices are connected via edges labelled with 0, while the other two edges have non-zero labels encoding the ordering.

S. Junges et al.

Fig. 11. DFT (a) and its labelled graph representation (b)

An edge-order preserving mapping constructs the edge labels in the order of the successor-sequence in a DFT. For encoding, we simply count the children from left to right; this is a trivial encoding. As rewriting may delete edges, we need a slightly more general definition for decoding.

**Definition 4.1** (*Edge-order preserving*) Let  $F = (V, \sigma, Tp, \Theta, top)$  be a DFT. A mapping  $o: E(\sigma) \to \mathbb{N}$  is *edge* order preserving if for each  $v \in V$  with  $1 \le i < j \le |\text{child}(v)|$  it holds that

$o((v, \sigma(v)_i)) < o((v, \sigma(v)_j)).$

If for all  $v \in V$  and  $1 \le i \le |\operatorname{child}(v)|$  we have  $o(v, \sigma(v)_i) = i$ , then we call o trivial.

**Definition 4.2** (*Labelled graph of a* DFT) Let DFT  $F = (V, \sigma, Tp, \Theta, top)$  and *o* be a trivial edge order preserving mapping. The *DFT graph representation for* F is the labelled graph  $\mathcal{F} = (V_{\mathcal{F}}, E_{\mathcal{F}}, \text{src, tar, lab})$  over ((BasicEvents  $\cup \{0\} \cup \text{Gates} \cup \text{Leaves} \cup \{0, top\}$ ),  $\mathbb{N}$ ) with

- $V_{\mathcal{F}} = (V \times \{1, 2\}) \cup (F_{\mathsf{EE}} \times \{3\}) \cup \{(top, 4)\},\$

- $E_{\mathcal{F}} = \{ \langle (v, 1), (v', 1) \rangle \mid (v, v') \in E(\sigma) \}$   $\cup \{ \langle (v, 1), (v, 2) \rangle \mid v \in V \}$   $\cup \{ \langle (v, 1), (v, 3) \rangle \mid v \in F_{\mathsf{EE}} \}$  $\cup \{ \langle (top, 1), (top, 4) \rangle \}$

- $\operatorname{src}_{\mathcal{F}}(\langle w, w' \rangle) = w$  $\operatorname{tar}_{\mathcal{F}}(\langle w, w' \rangle) = w'$

- The vertex labelling function  $lab_v$  is given by

$$(v, 1) \mapsto 0$$

$$(v, 2) \mapsto Tp(v)$$

$$(v, 3) \mapsto \begin{cases} \Theta(v) & \text{if } v \in \text{Dom}(\Theta) \\ 0 & \text{else.} \end{cases}$$

$$(top, 4) \mapsto top$$

• The edge labelling function  $lab_e$  is given by

$$\begin{array}{l} \langle (v,1), (v',1) \rangle \mapsto o((v,v')) \\ \langle (v,1), (v,2) \rangle \mapsto 0 \\ \langle (v,1), (v,3) \rangle \mapsto 0 \\ \langle (top,1), (top,4) \rangle \mapsto 0. \end{array}$$

Fig. 12. The L and R subDFTs of the subsumption rule

#### 4.3. Rewriting DFTs

The core of a DFT rewrite rule consists of the two (sub)DFTs, representing the left- and right-hand side of the rule. SubDFTs do neither contain a *top* node, nor contain an attachment function. These restrictions allow simplifications, while still allowing to rewrite DFTs into equivalent DFTs ranging over the same set of basic events. For example, Fig. 12 displays the left- and right-hand side for the rewrite rule from Example 4.1. Here, the EEs from the example are generalised to be of arbitrary type; this is indicated by a triangle. We refer to these rules as *structural rules* as they only change the structure of the DFT.

**Definition 4.3** (*subDFT*) Let DFT  $F = (V, \sigma, Tp, \Theta, top)$ . A *subDFT of* F is a tuple  $X = (V_X, \sigma_X, Tp_X^{\sharp})$  with  $V_X \subseteq V, \sigma_X = \sigma | V_X$  and  $Tp_X^{\sharp} = Tp | Z$  where  $Z \subseteq V_X$ .  $Y = (V_Y, \sigma_Y, Tp_Y^{\sharp})$  is called a *subDFT of* F if it is a subDFT of some DFT F; Y is well-formed if it is a subDFT of a well-formed DFT.

All notions and notations for DFTs are also used for subDFTs. We emphasise that the subDFTs do not contain any information about basic events or their failure rates.

Like graph rewrite rules, a DFT rewrite rule consists of an interface, left- and right-hand side graphs and two homomorphisms. Additionally, DFT rewrite rules contain a context restriction—defined as a set of DFTs; DFTs which violate the restriction—i.e. DFTs in the set—are not amenable to rewriting by the corresponding rewrite rule. The interface only consists of elements; partitioned into an input (sinks in the graph) and an output interface. We formally define a rewrite rule as follows where we impose some restrictions on the interfaces, which we discuss later on.

**Definition 4.4** ((*Structural*) DFT rewrite rule) A DFT rewrite rule is a tuple ( $V_i$ ,  $V_o$ , L, R, H,  $\mathfrak{C}$ ) with

- A set of *input elements*  $V_i$ .

- A set of *output elements*  $V_{\mathfrak{o}}$  with  $V_{\mathfrak{i}} \cap V_{\mathfrak{o}} = \emptyset$ .

- A well-formed matching subDFT  $L = (V_L, \sigma_L, Tp_L^{\sharp})$ .

- A well-formed result subDFT  $R = (V_R, \sigma_R, T p_R^{\sharp})$ .

- Two graph morphisms  $H = \{h_l, h_r\}$  with

- an embedding  $h_l: V_i \cup V_o \to L$ , and

- a homomorphism  $h_r: V_i \cup V_o \to R$  such that  $h_r \mid V_i$  is injective.

- A context restriction set  $\mathfrak{C} = \{(F_i, \zeta_i) \mid i \in \mathbb{N}, F_i \text{ a DFT}, \zeta_i \colon L \twoheadrightarrow V\}$  of embargo DFTs where  $\zeta_i$  is a graph homomorphism for each  $i \in \mathbb{N}$ ,

such that the following conditions hold:

- 1. The left-hand side elements without children are the input elements:  $h_l(V_i) = \{v \in L \mid \text{child}(v) = \emptyset\}$ .

- 2. No children are added to input elements:  $\forall v \in h_r(V_i)$ . child $(v) = \emptyset$ .

- 3. All elements in L that are not input elements are typed:  $V_L \setminus h_l(V_i) \subseteq \text{Dom}(Tp_L^{\sharp})$ .

- 4. Typing of input elements in L and R agree:  $\forall v \in V_i$ .  $Tp_L^{\sharp}(h_l(v)) = Tp_R^{\sharp}(h_r(v))$ .

- 5. Output elements are not typed as FDEPs:  $\forall v \in V_{\mathfrak{o}}$ .  $Tp_L^{\sharp}(h_l(v)) \neq \mathsf{FDEP} \neq Tp_R^{\sharp}(h_r(v))$ .

We abbreviate DFT rewrite rule  $(V_i, V_o, L, R, H, \mathfrak{C})$  by  $(L \leftarrow (V_i \cup V_o) \rightarrow R, \mathfrak{C})$ . By slight abuse of notation, we use  $h_l(h_r)$  also to denote the embedding from  $V_i \cup V_o$  into  $\mathcal{L}(\mathcal{R})$ .

**Example 4.3** Consider the subsumption rule from Example 4.1, where we argued that the rule is not contextfree. Recall that Fig. 12 displays the left- and right subDFT where a triangle depicts an untyped element. Let  $V_i = \{C, D\}$  and  $V_o = \{A\}$ . The homomorphism  $h_l$  is a trivial embedding (the identifiers share the same name). The homomorphism  $h_r$  is given by  $A \mapsto A', C \mapsto C', D \mapsto D'$ . Furthermore,

$$L = (\{A, B, C, D\}, \{A \mapsto CB, B \mapsto CD, C \mapsto \varepsilon, D \mapsto \varepsilon\}, \{A \mapsto \mathsf{OR}, B \mapsto \mathsf{AND}\})$$

and

$$R = (\{A', C', D'\}, \{A' \mapsto C', C' \mapsto \varepsilon, D' \mapsto \varepsilon\}, \{A' \mapsto \mathsf{OR}\}).$$

Note that we cannot match B on an element with other successors than the element matched by A. If we would allow such match, a dangling edge would result, as we remove the element matched by B.

The context restriction is aimed to ensure that problems as in Example 4.1 cannot occur. For the sake of simplicity, we impose a rather strong restriction; it guarantees that (a) the element matched by D does not have any predecessors after rewriting—by ensuring it has only one predecessor during matching, and (b) the matched element of D is an EE. This means that D is an EE which is independent of other parts after rewriting. Thus, any issues where D is not activated do not play a role here. Formally, the context restriction is given as

$\mathfrak{C} = \{(F, \zeta) \in \text{DFT} \times (\text{subDFT} \to \text{DFT}) \mid \text{parent}(\zeta(D)) \neq \{\zeta(B)\} \lor Tp(\zeta(D)) \neq \text{EE}\}.$

It follows that all conditions from Definition 4.4 are fulfilled; this thus defines a DFT rewrite rule.

The semantics of DFT rewrite rules, i.e., (1) when can a rule be applied? and (2) what is result of applying a rule?, are given by a reduction to graph rewriting; cf. Sect. 4.4. We introduce the important notions here on a more intuitive level. A rule can be *matched* on a DFT F if the left subDFT L is a substructure of F. The elements corresponding to L in F are called the matched elements; other elements in F are called *unmatched*. As we want to prevent rules from being applicable in certain contexts, rewrite rules have a possibly empty, possibly infinite, set of DFTs on which they cannot be applied, called *context restrictions*. In these DFTs, we have to mark where the match cannot be applied, which is done by a homomorphism from the left of the DFT in which the rule cannot be applied. If the DFT which we want to match corresponds to one of the DFTs in the context restriction, we call the DFT from the context restriction an *effective embargo*. In absence of an effective embargo, a *successful match* exists, together with a *matching homomorphism*. The replacement of L by the R in a successful match is called a *rewrite step*.

*Remark* **2** We usually do not give the context restrictions as an explicit set, but rather by characterising which DFTs should be excluded. The context restriction is then the set of all DFTs which satisfy the characterisation. When operationalising this in GROOVE in Sect. 6, we make use of the advanced features that GROOVE [GdMR<sup>+</sup>12] has to embed these restrictions into the rewriting directly.

**Input- vs. output-interface.** To ease the correctness proofs of the DFT rewrite rules, we distinguish an input- and output-interface. Elements in the input- and output-interface are called *input-* and *output-elements*, respectively. Roughly speaking, input-elements are the start of failure propagations through the subDFTs, while output-elements are the endpoints. Intuitively, on rewriting DFT F into F' by replacing subDFT L by R, the elements in the interface are kept untouched—as in standard graph rewriting. In particular, only elements matched by interface vertices in F can have unmatched successors or unmatched predecessors. All successors of output-elements are not restricted in the type of connections to unmatched elements. As they are the starting point of failure propagation, we require them to only have unmatched successors; moreover, they should fail as before (based on the failure-behaviour of their children). Thus, changing the type of input elements is forbidden.

**Correctness of DFT rules.** So far, a rewrite rule is allowed to take any form; in particular it can change the semantics. In Sect. 5.3, we give 29 families of rules. All those rules preserve the reliability and the mean time to failure; that is if F is rewritten to F' by any of the rules, then F and F' give rise to the same reliability and MTTF.

#### 4.4. Graph rewriting for DFTs

In order to formalise the rewriting of DFTs, we reduce this to the well-established area of graph rewriting; this is depicted in Fig. 13. Each DFT has an unique—up to isomorphism—graph representation. Moreover, a graph

Fig. 13. Formalise DFT rewriting via standard graph rewriting

Fig. 14. Graph representation for the DFT subsumption rule in Fig. 12

representation yields an—up to isomorphism—unique DFT. Every DFT rewrite rule can be translated into a DPO graph rewrite rule. A DFT rewrite rule is then matched if the left-hand side graph in the corresponding graph rewrite rule can be matched against the graph representation of the DFT. The effect of the application of a DFT rewrite rule is given by applying the corresponding graph rewrite rule on an encoded DFT. The resulting graph can be decoded, yielding a DFT, which *by definition* is the result of the rewrite step. The remainder of the section formalises this approach.

## 4.4.1. Encoding structural rewrite rules as graph rewrite rules

**Definition 4.5** (*The graph rewrite rule of a* DFT *rewrite rule*) The *corresponding graph rewrite rule* of DFT rewrite rule ( $V_i$ ,  $V_o$ , L, R, { $h_l$ ,  $h_r$ },  $\mathfrak{C}$ ) equals ( $\mathcal{L}$ ,  $V_i \cup V_o$ ,  $\mathcal{R}$ ,  $h_l$ ,  $h_r$ ) where  $\mathcal{L}$  and  $\mathcal{R}$  are the graphs that correspond to DFTs L and R, respectively.

The definition above does not add the carries of the interface elements to the interface of the graph rewrite rule. This is not important, as the carries are only connected to these interface vertices. With this graph rewrite rule, the carries are deleted and added afterwards, thereby not changing them. Note that the attachment function is untouched. Thus, we cannot delete any EEs with attached basic events. Furthermore, the context restrictions are not explicitly reflected in the graph rewrite rule. Graph rewriting has been extended to feature context restrictions (often referred to as negative application conditions), but a translation into these rules is not straightforward. Rather, we check the context restriction on the DFT representation and then apply the rule on the graph representation of a DFT only if the context restriction is met.

**Example 4.4** Consider the DFT rewrite rule in Fig. 12. Its graph rewrite rule is given in Fig. 14. The actual homomorphisms between the vertices are given by their relative position in the graph. We see that the two type-less elements do not have carries attached. The graph rewriting removes everything but the tree vertices corresponding to the elements. In particular, it also removes the type of the topmost element. On the right-hand side, this type is added again.

**Definition 4.6** (*Match*) Let *F* be a DFT with graph representation  $\mathcal{F}$  and rewrite rule  $\mathfrak{r} = (L \leftarrow (V_i \cup V_o) \rightarrow R, \mathfrak{C})$ . Injective graph morphism  $\kappa : \mathcal{L} \twoheadrightarrow \mathcal{F}$  is a *rule match morphism* if it satisfies:

- 1. the dangling edge condition (cf. page 14).

- 2. no successors of output elements are deleted:  $\forall v \in V_{o}$ . | OutV(v) |=| OutV( $\kappa(v)$ ) |.

For rule match morphism  $\kappa$ ,  $\kappa(\mathcal{L})$  is called a *matched graph*,  $\kappa(V_i \cup V_o)$  the *match glue*, and  $\mathfrak{r}$  a *matching rule*.

Note that context restrictions are ignored here; they are captured just below.

Fig. 15. A small sample DFT with a dispensable EE

**Definition 4.7** (*Effective embargo*) Let  $\kappa$  be a rule match morphism on F. The embargo DFT  $F_i$  is called *effective* if for some injective homomorphism h from  $F_i$  to F it holds:

$h(\zeta_i(V_i)) = \kappa(h_i(V_i))$  and  $h(\zeta_i(V_o)) = \kappa(h_o(V_o)).$

**Definition 4.8** (*Successful match*) A matching rule is *successful*, if no  $\mathfrak{C}_i$  is an effective embargo.

**Definition 4.9** (DFT *rewrite step*) Let  $\mathfrak{r} = (L \leftarrow (V_i \cup V_o) \rightarrow R, \mathfrak{C})$  be a rewrite rule and F and F' DFTs with graph representations  $\mathcal{F}$  and  $\mathcal{F}'$ . Let **gr** be the corresponding graph rewrite rule of  $\mathfrak{r}$ . Let L be successfully matched in F by the graph morphism  $\kappa$ . Then F is *rewritten* by  $\mathfrak{r}$  using  $\kappa$  to F' if  $\mathcal{F} \xrightarrow{\mathsf{gr}} \mathcal{F}'$  is a graph rewrite step. The tuple  $(F, \mathfrak{r}, \kappa, F')$  is a (DFT) rewrite step.

The following result asserts that the outcome of a rewrite step again encodes a DFT. We state this result without formal proof; a proof is provided in [Jun15].

**Theorem 4.1** For rewrite step  $(F, \mathfrak{r}, \kappa, F')$ , the graph  $\mathcal{F}'$  of DFT F' is a valid DFT encoding.

## 4.4.2. Beyond structural rules

We discuss two rewrite steps for removing and merging EEs with attached basic events, respectively. The former reduces the set of basic events the DFT ranges over, the second requires a change of the set of basic events the DFT ranges over.

**Removing EEs.** Event elements that are not connected to the remainder of the DFT can be removed. Removal of EEs generates DFTs which do not range over the same set of basic events as original DFTs, therefore they are outside of our framework of structured DFT rewrite rules presented so far.

**Definition 4.10** (*Dispensable* EEs) Let  $F = (V, \sigma, Tp, \Theta, top)$  be a DFT. An event element  $v \in F_{EE}$  is *dispensable* in F if parent(v) =  $\emptyset$  and  $v \neq top$ .

Figure 15 shows a simple DFT where C is a dispensable EE. The DFT fails if both A and B have failed. The elimination aims to remove a EE v from the DFT. Therefore, we would have to make sure that

- 1. We update all parents to reflect that v is no longer present.

- 2. We update all incoming FDEPs as they can no longer trigger v.

To address (1), we replace the event element by a  $CONST(\perp)$  element, which in turn may be eliminated by structural rules that also update the parents accordingly. To address (2), we prevent any FDEPs from being present at the first place (notice that parent(v) =  $\emptyset$ ), and require structural rules to eliminate the FDEPs before eliminating the EE.

**Definition 4.11** (*Eliminating a dispensable* EE) Let  $F = (V, \sigma, Tp, \Theta, top)$  be a DFT and v be an dispensable EE in F. The removal of v in F results in the DFT

$$F' = (V, \sigma, Tp \setminus \{v \mapsto \mathsf{EE}\} \cup \{v \mapsto \mathsf{CONST}(\bot)\}, \Theta \mid (V \setminus \{v\}), top).$$

Evidently, the removal of the dispensable EEs preserves reliability and MTTF of DFTs.

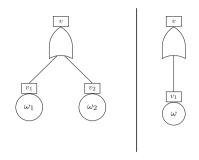

Fig. 16. Merging two EEs with (only) a common OR-gate. Failure rate and dormancy factor of  $\omega$  are given in Theorem 4.2

**Lemma 4.1** Let F be a DFT and v a dispensable EE in F. Furthermore, let F' be the result of the dispensable EE removal of v. It holds that  $RELY_F = RELY_{F'}$  and  $MTTF_F = MTTF_{F'}$ .

DFTs where superfluous EEs occur in another fashion, i.e., connected to other elements, can be rewritten into DFTs where elements are disconnected by the use of structural rules. Thus, there is no need to generalise this rule.

**Merging EEs.** The measures **RELY** and **MTTF** are defined independent of the identity of the basic events; therefore, we can also modify these events and preserve **RELY** and **MTTF**. The basic idea is depicted in Fig. 16. Two EEs  $(v_1, v_2)$  whose attached basic events  $(\omega_1, \omega_2)$  have failure rates of  $\lambda_{\omega_1}$  and  $\lambda_{\omega_2}$ , respectively, can be merged into a single EE with an attached basic event  $\omega$  with a failure rate  $\lambda_{\omega} = \lambda_{\omega_1} + \lambda_{\omega_2}$ . This is applicable if the EEs are not connected to any other gates. The failure distribution of the OR-gate is given by the minimum over the children. As the children are exponentially distributed, it follows that the OR-gate is also exponentially distributed.

We focus on the binary case, as the *n*-ary case can be reduced to several instances of the binary case in combination with the structural rewrite Rule 5.

**Definition 4.12** (Independent binary OR/EE) Let  $F = (V, \sigma, Tp, \Theta, top)$  be a DFT and  $v \in F_{OR}$  such that  $child(v) = \{v_1, v_2\} \subseteq F_{EE}$  and  $v_2 \neq top$ . Let  $parent(v_1) = parent(v_2) = \{v\}$ . Then  $(v, v_1, v_2)$  is an independent binary OR/EE sequence.

We want to collapse the two EEs into one; and do this by eliminating the second. We update the successor function of the OR-gate: It no longer has two children, instead it has  $v_1$  as only child. We then update the attachment function:  $v_1$  has now  $\omega$  attached, and notice that  $v_2$  no longer occurs in the DFT.

**Definition 4.13** (DFT *obtained by collapsing* OR/EE) Given a DFT *F* with the independent binary OR/EE sequence  $(v, v_1, v_2)$  and  $\{\omega, \omega_1, \omega_2\} \subseteq$  BasicEvents with  $\Theta(v_i) = \omega_i$  for  $i \in \{1, 2\}$  and  $\Theta(x) \neq \omega$  for all  $x \in V$ . Let  $\lambda_{\omega_1}, \alpha_{\omega_1}, \lambda_{\omega_2}, \alpha_{\omega_2}$  be the failure rate and dormancy factor of  $\omega_1, \omega_2$ , respectively. Let  $\omega$  have failure rate

$\lambda_{\omega} = \lambda_{\omega_1} + \lambda_{\omega_2}$  and dormancy factor  $\alpha_{\omega} = \frac{\alpha_{\omega_1} \lambda_{\omega_1} + \alpha_{\omega_2} \lambda_{\omega_2}}{\lambda_{\omega}}$ . Collapsing  $(v, v_1, v_2)$  in F yields the DFT F' with

$F' = (V \setminus \{v_2\}, \sigma \setminus \{v \mapsto v_1 v_2\} \cup \{v \mapsto v_1\}, Tp \mid V', \Theta' \cup \{v_1 \mapsto \omega\}, top)$

and  $\Theta'(v') = \Theta(v')$  for  $v' \in V \setminus \{v_1, v_2\}$  and  $\Theta'(v_1) = \omega$ .

For convenience, we do not remove the OR-gate; OR-gates with single successors can be eliminated by structural rules.

**Lemma 4.2** Given a DFT F with the independent binary OR/EE sequence  $(v, v_1, v_2)$ . Let F' be the DFT obtained from F by collapsing  $(v, v_1, v_2)$ . Then:  $MTTF_F = MTTF_{F'}$  and  $RELY_F = RELY_{F'}$ .

The proof of this lemma is rather straightforward and omitted. Note that introducing new EEs with new failure rates goes beyond standard graph rewriting, but is easily integrated in the GROOVE framework (cf. Sect. 6).

The merging rule presented here could be generalised into an additional set of rules, orthogonal to the earlier presented structural rules on DFTs. First of all, we observe that a (deterministic) DFT encodes a phase-type distribution [Neu94]. Obviously, there exist several DFTs which encode the same phase-type distribution, see the lemma above for an example. Each subtrees also encodes a phase-type distribution, given by a DFT which is isomorphic to the subtree. Such a subtree could thus be replaced by another DFT which encodes the same phase-type distribution without affecting the host DFT.

S. Junges et al.

Fig. 17. Invalid syntax due to merging spare modules

This allows for an automated proof-scheme for replacement of independent subDFTs by other DFTs; using work on the reduction of acyclic phase-type distributions on the CTMC level [PH08].

#### 4.5. Preserving well-formedness

In the last part of this section, we discuss the preservation of well-formedness by the DFT rewrite rules. Applying the rewrite rules on well-formed DFTs may result in a DFT that is not well-formed, as shown by the two examples below. The first example shows that rewriting may introduce dependencies between primary and spare children of SPARE-gates; the second one that rewriting may introduce loops.