# Fault-based Conformance Testing in Practice

Martin Weiglhofer and Bernhard Aichernig and Franz Wotawa

Institute for Software Technology - Graz University of Technology Inffeldgasse 16b/II - 8010 Graz - Austria

**Abstract** Conforming to protocol specifications is a critical issue in modern distributed software systems. Nowadays, complex service infrastructures, such as Voice-over-IP systems, are usually built by combining components of different vendors. If the components do not correctly implement the various protocol specifications, failures will certainly occur. In the case of emergency calls this may be even life-threatening. Functional black-box conformance testing, where one checks the conformance of the implemented protocol to a specification becomes therefore a major issue. In this work, we report on our experiences and findings when applying fault-based conformance testing to an industrial application. Besides a discussion on modeling and simplifications we present a technique that prevents an application from implementing particular faults. Faults are modeled at the level of the specification. We show how such a technique can be adapted to specifications with large state spaces and present results obtained when applying our technique to the Session Initiation Protocol and to the Conference Protocol. Finally, we compare our results to random and scenario based testing. **Key words:** fault-based testing, mutation testing, input-output conformance, ioco

## 1 Introduction

Validation and verification is an important task in the development of safety-critical and highly available software systems. Modern distributed systems often rely on the communication of standardized protocols implemented by different vendors. To ensure a proper cooperation of the different implementations they all must conform to the protocol specification. That is, one needs to check the conformance of the observable behavior of implementations. By considering the implementation as a black-box, i.e. without any access to the source code, one can validate the observable behavior with respect to a specification. Functional black-box testing is the method of choice for such end-to-end testing.

However, testing if conducted thoroughly and systematic is a rather tedious and time-consuming task. A formal notion of conformance and mature research prototypes suggest the application of formal methods for automatic test case generation. However, in practice there are still some challenges and issues that need to be considered:

**Test case selection** The early work on formal conformance testing in the area of distributed systems was mainly concerned with the soundness and completeness of the testing theory. Since the models were finite labeled transition systems, the problem of how to select a manageable subset out of the exhaustive test set was not

<sup>‡</sup> Corresponding author: Martin Weiglhofer, Institute for Software Technology, Graz University of Technology, Inffeldgasse 16b/II, 8010 Graz, Austria, e-mail: weiglhofer@ist.tugraz.at.

a major concern. However, in practice time and resources for testing are usually very limited. Thus, there is a need for selecting a proper subset of test cases.

Identifying test purposes Test purposes, i.e. formalized test objectives, have been introduced to allow efficient test case generation for large specifications. Unfortunately, this still leaves the tester with the task of writing test purposes, which might turn out to be rather difficult if thorough testing is required. For example, du Bousquet et al. [dBRS<sup>+</sup>00] report that even after ten hours of manual test purpose design they failed to find a set of test purposes that would detect all mutants of a given implementation.

In our approach, we want to support the tester in formalizing test purposes, by turning his focus on possible faults. Possible faults can be anticipated by inspecting a specification, by using domain knowledge, or by heuristic fault injection operators. In all cases, the fault is modeled at the specification level by altering the specification syntactically. We call this altered version a mutant. The idea, is to generate test cases that would find such faults in the implementation.

- **Equivalent mutants** A common problem with this approach is known as the Equivalent Mutant Problem. Not all mutations represent actual faults that can be observed at the interface level. Thus, no test case exists that can distinguish the original from such an equivalent mutant. On the specification level, equivalence/preorder checkers can be used to eliminate such equivalent mutants. The problem is which equivalence/preorder relation is appropriate for our purposes. Once, the relation is fixed, the problem is theoretically solved.

- **Applicability to industrial specifications** In order to detect equivalent mutants one needs to compare the complete state spaces of the mutant and the original specification. Due to time and resource limits this is often infeasible for industrial specification. However, equivalent mutants do not lead to useful test cases because they cannot be distinguished from the specification. Test cases derived from such mutants do not improve test suites. This paper presents an approach applicable to large specifications while guaranteeing that no redundant test cases for equivalent mutants are generated.

- Automated test case generation The technique should automatically generate test cases. Many use the counter examples (or witnesses) produced by a model checker as test cases. A counter example is not a test case in the traditional sense. A test case should provide the stimuli and the responses for a system. However, a counterexample exemplifies only one possible choice of computation (a path). In case of non-determinism involved this is not sufficient for a test case, since a test case should predict and take care of all possible responses, as well as reject wrong responses.

This paper presents a fully automated, fault-based, practical approach for test case selection based on LOTOS specifications. The presented approach focuses on simple faults on the specification's level. Given a specification, such faults are inserted automatically into the specification. Faulty specifications are called mutants. Note that there is only one fault per mutant. A conformance check between a faulty specification and the original specification leads to a (linear) counterexample if the mutant does not conform to the specification. Such a linear counterexample is not a valid test case for non-deterministic systems. Thus, we use this counterexample as a high-level description of the testing goal, i.e. as a test purpose. The generated test purpose allows one the use of established tools for deriving test cases based on test purposes, e.g. TGV [JJ05], SAMSTAG [GHN93], or Microsoft's SPECEXPLORER [VCG<sup>+</sup>08]. The presented approach offers the advantages of mutation based test selection strategies together with the efficiency of test purpose based test derivation algorithms.

This paper is based on our previous work [AD06, APWW07a, APWW07b, AWW08, WW08a, WW08b], which it extends with:

- Summing up our experiences of modeling and fault-based testing on industrial applications,

- a detailed discussion of formalizing the Session Initiation Protocol (SIP) in terms of a LOTOS specification,

- a new approach for handling specifications with large, industrial scale, state spaces,

- new experimental results showing the practicability when applying the presented approach to the Session Initiation Protocol,

- and results obtained by applying our fault-based testing technique to an additional protocol specification, the Conference Protocol [TPHT96].

**Case Study** Our main application domain is testing in the context of Voice-over-IP. One elementary protocol within the Voice-over-IP landscape is the Session Initiation Protocol.

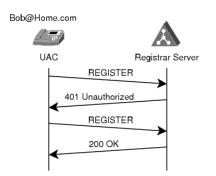

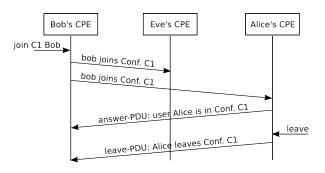

The Session Initiation Protocol (SIP) [RSC<sup>+</sup>02] handles communication sessions between two end points. The focus of SIP is the signaling part of a communication session independent of the used media type between two end points. More precisely, SIP provides communication mechanisms for user management and for session management. User management comprises the determination of the location of the end system and the determination of the availability of the user. Session management includes the establishment of sessions, transfer of sessions, termination of sessions, and modification of session parameters. SIP defines various entities that are used within a SIP network. One of these entities is the *Registrar*, which is responsible for maintaining location information of users. An example call flow of the registration process is shown in Figure 1. In this example, Bob tries to register his current device as end point for his address Bob@home.com. Because the server needs authentication, it returns "401 Unauthorized". This message contains a digest which must be used to re-send the register request. The second request contains the digest and the user's authentication credentials, and the Registrar accepts it and answers with "200 OK". For a full description of SIP we refer to  $[RSC^+02]$ .

The SIP Registrar will serve as a running example in this paper in order to discuss various aspects of our approach.

This paper is organized as follows. Section 2 gives a brief overview of formal conformance testing, including an instantiation of this formal testing framework based on labeled transition systems and an introduction to input-output conformance testing. Section 3 reviews the LOTOS specification language, including an example specification based on parts of the Session Initiation Protocol. Furthermore, Section 3 discusses the

Fig. 1. Simple Call-Flow of the registration process.

need and the usage of simplifications during modeling. Section 4 shows how to apply fault-based conformance testing to industrial scale LOTOS specifications, including mutation operators for LOTOS specifications. Furthermore, this section summarizes our approach for efficient on-the-fly input-output conformance checking and extends our previous work by introducing bounded **ioco**. We applied our technique to two different specifications. Section 5 presents the obtained results and compares the approach presented in this paper with other test case selection strategies. We review related work in Section 6 and conclude in Section 7.

# 2 Formal Conformance Testing

An overall framework of formal conformance testing has been proposed in [IJW97, HHT96]. The central element within this conformance testing framework is the definition of what is a correct implementation of a formal specification. This defines a conformance relation. To define such conformance relations it is assumed that there exists a formal specification of the required behavior, i.e.,  $s \in SPECS$ . The set SPECS is the set of all possible specifications that can be expressed using a particular specification language.

In addition to the specification, there is the implementation under test  $IUT \in IMPS$ , which denotes the real, physical implementation. IMPS is the universe of all possible implementations. We want to formally reason about the correctness of the concrete implementation IUT with respect to the specification s. Thus, as a common testing hypothesis [Tre92, Ber91] it is assumed that every implementation can be modeled by a formal object  $m_{IUT} \in MODS$ . MODS denotes the set of all models. Note that it is not assumed that this model is known, only its existence is required.

Conformance is expressed as a relation between formal models of implementations and specifications, i.e.,

$$\operatorname{imp} \subseteq MODS \times SPECS$$

As each model  $m_{IUT} \in MODS$  represents a concrete implementation  $iut \in IMPS$ a conformance relation **imp** allows one to formally reason about the correctness of the *iut* with respect to a specification  $s \in SPECS$ .

By applying inputs to the implementation and observing outputs, i.e. by testing, one wants to find non-conforming implementations. The universe of test cases is given by *TESTS*. Executing a test case  $t \in TESTS$  on an implementation leads to observations  $obs \subseteq OBS$ , where OBS denotes the universe of observations.

Formally, test case execution is modeled by a function  $exec : TESTS \times MODS \rightarrow OBS$ . Given a test case  $t \in TESTS$  and a model of an implementation  $m \in MODS$ , exec(t, m) gives the observations in OBS that result from executing t on the model m.

Finally, there is a function *verd* that assigns a verdict, i.e. pass or fail, to each observation:  $verd : OBS \rightarrow \{pass, fail\}$ . An implementation  $IUT \in IMPS$  passes a test suite  $TS \subseteq TESTS$  if test execution of all its test cases leads to an observation for which *verd* evaluates to **pass**. In practice, there is a third verdict, i.e. inconclusive, that is used for judging test executions [JJ05]. This verdict is used if the implementation has not done anything wrong but the responses of the IUT did not satisfy the test objective.

There are different types of models and conformance relations that can be seen as an instantiation of this formal conformance testing framework. For example, when one uses testing techniques based on finite state machines (FSMs) [LY96, HBH08] then *MODS* and *SPECS* are usually some sorts of FSMs. Usually, the considered conformance relation is some relation between the states of the implementation and the states of the specification (e.g. isomorphism).

Another instantiation of this formal testing framework uses labeled transition systems for representing specifications and models of implementations. There is a broad range of relations that have been defined for labeled transition systems, e.g. bisimulation equivalence [Mil90], failure equivalence and preorder [Hoa85], and refusal testing [Phi87], just to name a few.

One commonly used conformance relation is the input-output conformance relation (ioco) [Tre96]. This relation is designed for functional black box testing of systems with inputs and outputs. Inputs are under the control of the environment, i.e. the tester, while outputs are under the control of the implementation under test. ioco allows one to use incomplete specifications. The specifications and the implementations can be non-deterministic. Furthermore, the models used for ioco allow arbitrary interleaving of input and output. Finally, ioco considers the absence of outputs as error if this behavior is not allowed by the specification. These properties make input-output conformance testing applicable to practical applications.

## 2.1 Input-Output Conformance

The input-output conformance (**ioco**) relation [Tre96] expresses the conformance of implementations to their specifications where both are represented as labeled transition systems (LTS). Because we distinguish between inputs and outputs, the alphabet of an LTS is partitioned into inputs and outputs.

**Definition 1 (LTS with inputs and outputs).** A labeled transition system with inputs and outputs is a tuple  $M = (Q, L \cup \{\tau\}, \rightarrow, q_0)$ , where Q is a countable, non-empty set of states,  $L = L_I \cup L_U$  a finite alphabet, partitioned into two disjoint sets, where  $L_I$  and  $L_U$  are input and output alphabets, respectively.  $\tau \notin L$  is an unobservable action,  $\rightarrow \subseteq Q \times (L \cup \{\tau\}) \times Q$  is the transition relation, and  $q_0 \in Q$  is the initial state.

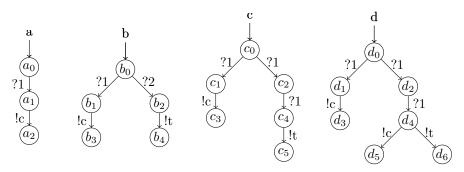

Fig. 2. Four labeled transition systems.

An LTS is *deterministic* if for any sequence of actions starting at the initial state there is at most one successor state.

We use the following common notations:

**Definition 2.** Given a labeled transition system  $M = (Q, L \cup \{\tau\}, \rightarrow, q_0)$  and let  $q, q', q_i \in Q, a_{(i)} \in L$  and  $\sigma \in L^*$ .

$$q \stackrel{a}{\rightarrow} q' =_{df} (q, a, q') \in \rightarrow$$

$$q \stackrel{a}{\rightarrow} =_{df} \exists q' \bullet (q, a, q') \in \rightarrow$$

$$q \stackrel{a}{\not\rightarrow} =_{df} \not\exists q' \bullet (q, a, q') \in \rightarrow$$

$$q \stackrel{a}{\not\rightarrow} =_{df} \not\exists q' \bullet (q, a, q') \in \rightarrow$$

$$q \stackrel{a}{\Rightarrow} q' =_{df} (q = q') \lor \exists q_0, \dots, q_n \bullet (q = q_0 \stackrel{\tau}{\rightarrow} q_1 \land \dots \land q_{n-1} \stackrel{\tau}{\rightarrow} q_n = q')$$

$$q \stackrel{a}{\Rightarrow} q' =_{df} \exists q_1, q_2 \bullet q \stackrel{\epsilon}{\Rightarrow} q_1 \stackrel{a}{\rightarrow} q_2 \stackrel{\epsilon}{\Rightarrow} q'$$

$$q \stackrel{a_1 \dots a_n}{\Rightarrow} q' =_{df} \exists q_0, \dots, q_n \bullet q = q_0 \stackrel{a_1}{\Rightarrow} q_1 \dots q_{n-1} \stackrel{a_n}{\Rightarrow} q_n = q'$$

$$q \stackrel{\sigma}{\Rightarrow} =_{df} \exists q' \bullet q \stackrel{\sigma}{\Rightarrow} q'$$

We use init(q) to denote the actions enabled in state q. Furthermore, we denote the set of states reachable by a particular trace  $\sigma$  by q after  $\sigma$ . More precisely,

**Definition 3.** Given an LTS  $M = (Q, L \cup \{\tau\}, \rightarrow, q_0)$  and  $q \in Q, S \subseteq Q, a \in L$ , and  $\sigma \in L^*$ :

$$init(q) =_{df} \{a | q \xrightarrow{a}\}$$

$$init(S) =_{df} \bigcup_{q \in S} init(q)$$

$$q \text{ after } \sigma =_{df} \{q' | q \xrightarrow{\sigma} q'\}$$

$$S \text{ after } \sigma =_{df} \bigcup_{q \in S} (q \text{ after } \sigma)$$

Note that we will not always distinguish between an LTS M and its initial state and write  $M \Rightarrow$  instead of  $q_0 \Rightarrow$ .

**Example 1.** Figure 2 shows four labeled transition systems representing a coffee/tee (c/t) vending machine. The input and output alphabets are given by  $L_I = \{1, 2\}$  and by  $L_U = \{c, t\}$ , i.e. one can insert one and two unit coins and the machine outputs

Fault-based Conformance Testing in Practice

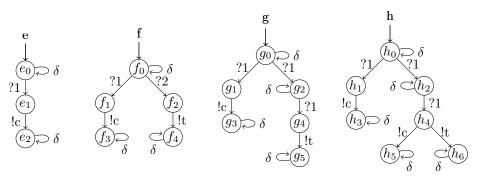

Fig. 3.  $\delta$ -annotated labeled transition systems.

coffee or tea. We denote input actions by the prefix "?", while output actions have the prefix "!". For example,  $a_0$  after  $\langle ?1 \rangle = \{a_1\}$  while  $c_0$  after  $\langle ?1 \rangle = \{c_1, c_2\}$ .  $\Box$

The **ioco** conformance relation employs the idea of observable quiescence. That is, it is assumed that a special action, i.e.  $\delta$ , is enabled in the case where the labeled transition system does not provide any output action. These  $\delta$ -labeled transitions allow to detect implementations that do not provide outputs while the specification requires some output (see Example 4:  $\neg(k \text{ ioco } e)$ ). The input output conformance relation identifies quiescent states as follows: A state q of a labeled transition system is quiescent if neither an output action nor an internal action ( $\tau$ ) is enabled in q.

**Definition 4.** Let M be a labeled transition system  $M = (Q, L \cup \{\tau\}, \rightarrow, q_0)$ , with  $L = L_I \cup L_U$ , such that  $L_I \cap L_U = \emptyset$ , then a state  $q \in Q$  is quiescent, denoted by  $\delta(q)$ , if  $\forall a \in L_U \cup \{\tau\} \bullet q \not\rightarrow$ .

By adding  $\delta$ -labeled transitions to LTSs the quiescence symbol can be used as any other action.

**Definition 5.** Let  $M = (Q, L \cup \{\tau\}, \rightarrow, q_0)$  be an LTS then  $M_{\delta} = (Q, L \cup \{\tau, \delta\}, \rightarrow \cup \rightarrow_{\delta}, q_0)$  where  $\rightarrow_{\delta} =_{d_f} \{q \xrightarrow{\delta} q | q \in Q \land \delta(q)\}$ . The suspension traces of  $M_{\delta}$  are  $Straces(M_{\delta}) =_{d_f} \{\sigma \in (L \cup \{\delta\})^* | q_0 \xrightarrow{\sigma} \}$ .

Unless otherwise indicated, from now on we include  $\delta$  in the transition relation of LTSs, i.e., we use  $M_{\delta}$  instead of M.

The class of labeled transition systems with inputs  $L_I$  and outputs in  $L_U$  (and with quiescence) is denoted by  $\mathcal{LTS}(L_I, L_U)$  [Tre96]. This is the universe of specifications, i.e.  $SPECS = \mathcal{LTS}(L_I, L_U)$ .

**Example 2.** Figure 3 shows the  $\delta$ -annotated LTSs for the LTSs illustrated in Figure 2. For example, the states  $g_0$ ,  $g_2$ ,  $g_3$ , and  $g_5$  are quiescent because they do not have outputs nor  $\tau$  actions.

Models for implementations in terms of the input-output conformance relation are input-output transition systems (IOTS). Recall that it is not assumed that this LTS is known in advance, but only its existence is required. Implementations are not allowed to refuse inputs, i.e. implementations are assumed to be input-enabled and so are their models. Note that specifications do not have to be input-enabled.

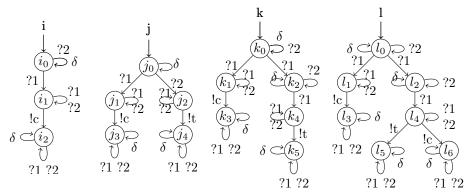

Fig. 4. Input-output transition systems.

**Definition 6 (IOTS).** An input-output transition system is an LTS  $M = (Q, L \cup \{\tau\}, \rightarrow, q_0)$ , with  $L = L_I \cup L_U$ , such that  $L_I \cap L_U = \emptyset$ , where all input actions are enabled (possibly preceded by  $\tau$ -transitions) in all states:  $\forall a \in L_I, \forall q \in Q \bullet q \stackrel{a}{\Longrightarrow}$ .  $\Box$

Note that this sort of input-enabledness, i.e. where  $\tau$ -labeled transitions may precede input actions ( $\forall a \in L_I, \forall q \in Q \bullet q \stackrel{a}{\Longrightarrow}$ ), is called *weak input-enabledness*. Contrary, strong input-enabledness requires that all input actions are enabled in all states, i.e.  $\forall a \in L_I, \forall q \in Q \bullet q \stackrel{a}{\Longrightarrow}$ .

The class of IOTSs with inputs  $L_I$  and outputs in  $L_U$  is given by  $\mathcal{IOTS}(L_I, L_U) \subseteq \mathcal{LTS}(L_I, L_U)$  [Tre96]. As IOTSs are used to formally reason about implementations, input-output transition systems are our implementation models, i.e.  $MODS = \mathcal{IOTS}(L_I, L_U)$  when instantiating the formal framework of conformance testing.

**Example 3.** Figure 4 depicts the IOTSs derived from the LTSs of Figure 3.  $\Box$

We use out(q) to denote the outputs at a state q.

**Definition 7.** Given a labeled transition system  $M = (Q, L \cup \{\tau, \delta\}, \rightarrow, q_0)$ , with  $L = L_I \cup L_U$ , such that  $L_I \cap L_U = \emptyset$ , let  $q \in Q$  and  $S \subseteq Q$ , then

$$out(q) =_{df} \{a \in L_U | q \xrightarrow{a} \} \cup \{\delta | \delta(q)\}$$

$out(S) =_{df} \bigcup_{q \in S} (out(q))$

Informally, the input-output conformance relation states that an implementation under test (IUT) conforms to a specification S iff the outputs of the IUT are outputs of S after an arbitrary suspension trace of S. Formally, **ioco** is defined as follows:

**Definition 8 (Input-output conformance).** Given a set of inputs  $L_I$  and a set of outputs  $L_U$  then  $\mathbf{ioco} \subseteq \mathcal{IOTS}(L_I, L_U) \times \mathcal{LTS}(L_I, L_U)$  is defined as:

$$IUT \text{ ioco } S =_{df} \forall \sigma \in Straces(S) \bullet out(IUT \text{ after } \sigma) \subseteq out(S \text{ after } \sigma) \square$$

**Example 4.** Consider the LTSs of Figure 3 to be specifications and let the IOTSs of Figure 4 be implementations. Then we have *i* **ioco** *e* and *j* **ioco** *f*. We also have *j* **ioco** *e* because  $\langle ?2 \rangle$  is not a trace of *e*. Thus, this branch is not relevant with respect

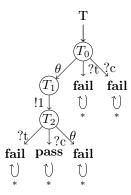

Fig. 5. Example of a test case.

to ioco. k does not conform to e, i.e.  $\neg(k \text{ ioco } e)$ , because  $out(k \text{ after } ?1) = \{!c, \delta\} \not\subseteq \{!c\} = out(e \text{ after } ?1)$ . Furthermore  $\neg(l \text{ ioco } e)$  because  $out(l \text{ after } ?1) = \{!c, \delta\} \not\subseteq \{!c\} = out(e \text{ after } ?1)$ . Due to the use of suspension traces we also have  $\neg(l \text{ ioco } k)$  because  $out(l \text{ after } ?1, \delta, ?1\rangle) = \{!c, !t\} \not\subseteq \{!t\} = out(k \text{ after } (?1, \delta, ?1\rangle)$ .

#### 2.2 Test Cases and Test Case Execution

By the use of a particular set of test cases one wants to test if a given implementation conforms to its specification. In the **ioco** framework a test case is a labeled transition system [Tre96]. In a test case the observation of  $\delta$  is implemented by  $\theta$ , i.e., test cases use  $\theta$ , to observe  $\delta$ . This is because, in practice  $\delta$  is a timeout, which is not a normal event that can be observed.  $\theta$  can be seen as the timer used to observe the occurrence of quiescence, i.e. the occurrence of  $\delta$ . Note that inputs of a test case are outputs of an IUT and vice versa.

**Definition 9 (Test case).** A test case T is an LTS  $T = (Q, L \cup \{\theta\}, \rightarrow, q_0)$ , with  $L = L_I \cup L_U$ , and  $L_I \cap L_U = \emptyset$ , such that (1) T is deterministic and has finite behavior; (2) Q contains sink states **pass** and **fail** (in **pass** and **fail** states a test case synchronizes on any action); and (3) for any state  $q \in Q$  where  $q \neq$  **pass** and  $q \neq$  **fail**, either  $init(q) = \{a\}$  for some  $a \in L_U$ , or  $init(q) = L_I \cup \{\theta\}$ .

$\mathcal{TEST}(L_U, L_I)$  denotes the class of test cases over  $L_U$  and  $L_I$ , i.e.  $TESTS = \mathcal{TEST}(L_U, L_I)$ . A test suite is a set of test cases.

**Example 5.** Figure 5 shows a test case satisfying Definition 9. In a state either inputs (outputs of the IUT) and the  $\theta$  event are enabled, or an output is enabled. The \*-labeled transitions in **pass** and **fail** states denote that in such states a test case synchronizes on any actions.

Running a test case  $t \in \mathcal{TEST}(L_U, L_I)$  against an implementation under test  $i \in \mathcal{TOTS}(L_I, L_U)$  is similar to the parallel composition of the test case and the implementation. The only difference is that  $\theta$  is used to observe  $\delta$ . Formally, running t on i is denoted by t]|i.

**Definition 10 (Synchronous execution).** Given a test case  $t \in \mathcal{TEST}(L_U, L_I)$ , an IUT  $i \in \mathcal{IOTS}(L_I, L_U)$ , and let  $a \in L_U \cup L_I$ , then the synchronous test case

execution operator ]| has the operational semantics defined by the following inference rules:

$$\frac{i \stackrel{\tau}{\longrightarrow} i'}{t\rceil |i \stackrel{\tau}{\longrightarrow} t\rceil |i'} \quad \frac{t \stackrel{a}{\longrightarrow} t', i \stackrel{a}{\longrightarrow} i'}{t\rceil |i \stackrel{a}{\longrightarrow} t'\rceil |i'} \quad \frac{t \stackrel{\theta}{\longrightarrow} t', i \stackrel{\delta}{\longrightarrow}}{t\rceil |i \stackrel{\theta}{\longrightarrow} t'\rceil |i}$$

A test run can always continue, i.e. there are no deadlocks. This is because a test case synchronizes on any action when a verdict state is reached. Formally, a test run is a trace of t |*i* leading to a verdict state (**pass**, **fail**) of t:

**Definition 11 (Test run).** Given a test case  $t \in \mathcal{TEST}(L_U, L_I)$  and an IUT  $i \in \mathcal{IOTS}(L_I, L_U)$ , then a test run  $\sigma \in L_U \cup L_I \cup \{\theta\}$  is given by:  $\exists i' \bullet t \rceil | i \stackrel{\sigma}{\Longrightarrow} \mathbf{pass} \rceil | i'$  or  $\exists i' \bullet t \rceil | i \stackrel{\sigma}{\Longrightarrow} \mathbf{fail} \rceil | i'$ .

An implementation i passes a test case iff all possible test runs lead to **pass** verdict states of the test case:

**Definition 12 (Passing).** Given an implementation  $i \in \mathcal{IOTS}(L_I, L_U)$  and a test case  $t \in \mathcal{TEST}(L_U, L_I)$ , then i passes  $t \Leftrightarrow_{df} \forall \sigma \in (L_I \cup L_U \cup \theta)^*, \forall i' \bullet t] | i \not\rightleftharpoons fail ] | i'$

**Example 6.** Running the test case of Figure 5 on the IUT *i* of Figure 4 leads to the following test runs:

$$\begin{array}{cccc} T_0 \rceil |i_0 & \stackrel{\langle \theta, !1, ?c \rangle}{\Longrightarrow} & \mathbf{pass} \rceil |i_2 \\ T_0 \rceil |i_0 & \stackrel{\langle \theta, !1, ?c, \theta \rangle}{\Longrightarrow} & \mathbf{pass} \rceil |i_2 \\ T_0 \rceil |i_0 & \stackrel{\langle \theta, !1, ?c, \theta, \theta \rangle}{\Longrightarrow} & \mathbf{pass} \rceil |i_2 \\ \dots \end{array}$$

Because all possible test runs lead to pass, we have i passes T.

Due to the structure of test cases, a test case may block outputs of an IUT. If a test case likes to provide a stimuli (input to the implementation) but the implementation opts for an output, the test case rules [PY02]. To overcome this issue, test cases have been made input-enabled recently [Tre08]. Input-enabled test cases do not block outputs of IUTs. However, such test cases comprise non-deterministic choices between inputs and outputs.

# 2.3 Test Case Generation

Among others, there are two test case generation strategies that have turned out to be well applicable in practice. First, there is the approach of selecting test cases randomly [Tre96]. Second, test cases are selected based on so called test purposes. A test purpose can be seen as a formal specification of a test case. Tools like SAMSTAG [GHN93], TGV [JJ05] and Microsoft's SPECEXPLORER [VCG<sup>+</sup>08] use test purposes for test generation. Our approach relies on TGV, where test purposes are defined as LTSs:

**Definition 13 (Test Purpose).** Given a specification S in the form of an LTS, a

test purpose is a deterministic LTS  $TP = (Q, L, \rightarrow, q_0)$ , equipped with two sets of trap states: Accept<sup>TP</sup> defines pass verdicts, and  $Refuse^{TP}$  limits the exploration of the graph S. Furthermore, TP is complete (i.e., it allows all actions in each state).

According to [JJ05] test synthesis within TGV is conducted as follows: Given a test purpose TP and a specification S, TGV calculates the synchronous product  $SP = S \times TP$ . The construction of SP is stopped in *Accept* and *Refuse* states as subsequent behaviors are not relevant to the test purpose. Then TGV marks all states where neither an output nor a  $\tau$ -labeled transition is possible by adding  $\delta$  labeled self-loops to these states (c.f. Definition 4). Before a test case is extracted, TGV obtains the observable behavior  $SP^{VIS}$  by making SP deterministic. Note that  $SP^{VIS}$  does not contain any  $\tau$ -labeled transitions.

A test case derived by TGV is controllable, i.e., it does not have to choose between sending different stimuli or between waiting for responses and sending stimuli. This is achieved by selecting traces from  $SP^{VIS}$  that lead to Accept states and pruning edges that violate the controllability property. Finally, the states of the test case are annotated with the verdicts pass, fail and inconclusive. Inconclusive verdicts denote that neither a pass nor a fail verdict has been reached but the implementation has chosen a trace that is not included in the traces selected by the test purpose.

Although test purposes are complete, i.e. they allow actions in each state, the derived test cases satisfy Definition 9. That is, a test case either provides a stimulus to the implementation or it accepts all possible responses from the implementation under test.

As a major strength of TGV, the test case synthesis is conducted on-the-fly: parts of S, SP, and  $SP^{VIS}$  are constructed only when needed. In practice, this allows one to apply TGV to large specifications.

#### 3 Modeling using LOTOS

Labeled transition systems are suitable models for representing test purposes, test cases, specifications, and implementations. However, for modeling large industrial systems it is impractical to write specifications in terms of labeled transition systems. Therefore, a specification language is needed having the semantics of labeled transition systems, but providing a simple syntax for writing large specifications. One such specification language is LOTOS, the language of temporal ordering specification [ISO89].

LOTOS is an ISO standard[ISO89]. LOTOS comprises two components: The first is based on the Calculus of Communication Systems [Mil80] (CCS) and deals with the behavioral description of a system, which is given in terms of processes, their behavior, and their interactions. The second component of LOTOS specifications is used to describe data structures and value expressions, and is based on the abstract data type language ACT ONE [EFH83].

The basic elements of a LOTOS specification are processes with a certain behavior expressed in terms of actions. An action is an expression over a process's gates, possibly equipped with values. Table 1 lists some of the main elements used to compose the behavior of a process. As listed in this table, an action is basically one of four expressions. There is the internal action i. There is the action without any parameters,

| Table 1. | Excerpt | of | LOTOS | behavior | elements. |

|----------|---------|----|-------|----------|-----------|

|----------|---------|----|-------|----------|-----------|

| Syntax                         | Meaning                       |

|--------------------------------|-------------------------------|

| i                              | internal action               |

| g                              | action, i.e. a process gate   |

| g !value                       | action offering a value       |

| g ?value:Type                  | action reading a value        |

| action; behavior               | action followed by a behavior |

| [guard] -> behavior            | guarded behavior              |

| behavior1 [] behavior2         | choice                        |

| behavior1    behavior2         | synchronization               |

| behavior1     behavior2        | interleaving                  |

| behavior1  [gate1,]  behavior2 | partial synchronization       |

| behavior1 [> behavior2         | disabled by second behavior   |

| behavior1 >> behavior2         | first enables second          |

| exit                           | exit                          |

| stop                           | stop, inaction                |

| <pre>proc[gate,](val,)</pre>   | process instantiation         |

| ( behavior )                   | grouping                      |

i.e. only the name of a process' gate. This simply expresses that the process offers this action for communication. Actions may offer values, i.e. g !value or actions may read values, i.e. g ?value.

Sequential composition is denoted by action; behavior, i.e. first the action is offered for communication and then the behavior is executed. The actions within a guarded behavior are only enabled if the guard evaluates to true.

A choice between two behaviors (behavior1 [] behavior2) expresses that the very first action of behavior1 and of behavior2 are offered for communication. Once, one of the offered actions is chosen by the environment the composed process behaves like behavior1 or behavior2. Basically, [] expresses external choice. Internal choice, i.e., a choice where a process itself decides on the offered actions, can be implemented using the special action *i*. *i* represents an internal transition, i.e. *i* results in a  $\tau$ -labeled transition within the underlying LTS semantics.

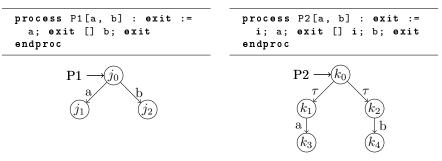

**Example 7.** Figure 6 illustrates the difference between internal and external choice in LOTOS and in the underlying labeled transition systems. The specification and its LTS shown on the left depict an external choice between the actions a and b. That is, in state  $j_0$  the environment can choose whether to synchronize on a or on b. On the contrary, the process P2 and its LTS depict an internal choice between a and b. That is, the system may internally decide to move to state  $k_1$  or to state  $k_2$ . In any case only one action is offered for communication.

LOTOS supports three different operators to express the parallel composition between processes, i.e., ||, |||, and |[...]|. The expression P1||P2 denotes the full synchronization on all gates of the two composed processes P1 and P2. The behavior of P1|||P2 is given by the unsynchronized interleaving of the behavior of P1 and of Fault-based Conformance Testing in Practice

Fig. 6. External and internal choice.

the behavior of P2. Finally, P1 | [...] |P2 is used to synchronize on a particular subset of the gates of the two processes. Note that this operator can be used to express the former two.

The enabling operator (>>) within a LOTOS specification states that a successful execution of the first process enables the following behavior block. In contrast to that, the disabling operator ([>) states that any action from the second behavior disables the execution of the first behavior. Finally, the behavioral part of LOTOS supports the definition of processes (for an example see Figure 6), instantiation of processes and grouping of behavior.

An abstract data type is given in terms of sorts, operations, and equations.

**Example 8.** Figure 7 shows the basic elements of data type definitions. This Configuration data type is part of our Session Initiation Protocol Registrar specification [Wei06] and is used to represent the list of configured users. Entries in this list are UserRecord-elements. A UserRecord is an abstract type representing a tuple. The tuple comprises the user identifier (UserId) and a Boolean flag indicating the authorization status of the user. If the flag is true, the user is allowed to modify the entries stored within the SIP Registrar.

The Configuration data type comprises the basic constructor nilCfg (Line 5), denoting an empty list, and the three operators addCfgEntry, getCfgEntry, and isin. isin is an infix operator while the other two operations use a prefix notation.

For example, the signature of the isin operator in Line 8 declares that this operator takes a user identifier (UserId) and a configuration list (Cfg) and returns a Boolean. The axioms of the isin operation, with the equations identifying Boolean terms (ofsort Bool), are read as follows: No element is in the empty list (Line 12). If the given user identifier (uid) is equal to the user identifier (Line 13) of an element elem, then uid isin addCfgEntry(elem, tail) is true for any remaining list tail. If the given uid is different to the identifier of the element elem, then the result of uid isin addCfgEntry(elem, tail) is true if uid is in the rest of the list, i.e. uid isin tail, and false otherwise (Line 16).

## 3.1 Modeling the Session Initiation Protocol in LOTOS

In this section we present parts of our Session Initiation Protocol (SIP) Registrar specification [Wei06] in order to exemplify the use of LOTOS.

A SIP Registrar provides its functionality through the maintenance of a state

```

type Configuration is UserRecord, Boolean

1

sorts

\mathbf{2}

Cfg

3

opns

4

nilCfg : -> Cfg

5

addCfgEntry : URec, Cfg -> Cfg

6

7

getCfgEntry

: UserId, Cfg

-> URec

8

_isin_ : UserId, Cfg -> Bool

9

eqns

forall uid: UserId, elem: URec, tail: Cfg

10

11

ofsort Bool

uid isin nilCfg = false;

12

(uid eq getUId(elem)) =>

13

14

(uid isin addCfgEntry(elem, tail)) = true;

(uid ne getUId(elem)) =>

15

(uid isin addCfgEntry(elem, tail)) = (uid isin tail);

16

17

ofsort URec

getCfgEntry(uid, nilCfg) = newURec(2 of UserId, true);

18

uid eq getUId(elem) =>

19

getCfgEntry(uid, addCfgEntry(elem, tail)) = elem;

20

uid ne getUId(elem) =>

21

getCfgEntry(uid, addCfgEntry(elem, tail)) =

22

getCfgEntry(uid, tail);

^{23}

24 endtype (* Cfg

*)

```

**Fig. 7.** A LOTOS abstract data type definition representing a list of configuration entries for our specification of a Session Initiation Protocol Registrar.

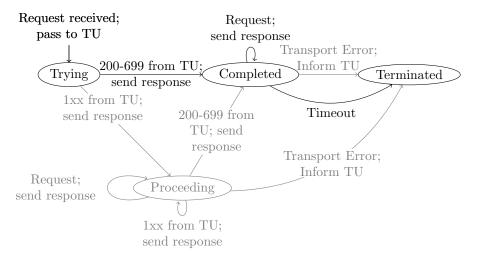

machine. Basically, this state machine is responsible for retransmission of responses of the SIP Registrar. Figure 8 shows the so called non-invite server transaction of a SIP Registrar. We abstracted from nodes and edges drawn in gray since they are not relevant or hard to consider within a model suited for testing this protocol.

Each REGISTER request is processed by its own state machine. As illustrated by Figure 8, an initial request is handed over to the transaction's user (TU), i.e. the Registrar core. Based on the header fields of the request the Registrar core determines a proper response and forwards the response to the state machine. Responses in the Session Initiation Protocol are identified by three digits. Since a Registrar never generates 1xx responses, our model does not include the gray edge from the *Trying*state to the *Proceeding*-state. Any other response, i.e.200-699, is forwarded to the initiator of the request (*send response*). The state machine then goes to its *Completed*state.

Once, the *Completed*-state is reached any request (which matches the transaction handled by this state machine) is answered with the last sent response (self-loop on the state *Completed*). After a particular amount of time, the state machine moves to the *Terminated*-state and the transaction is destroyed.

Figure 9 shows our LOTOS formalization of the transaction handling state machine. The state machine is represented by a single process (serverTransaction). This process communicates with the transaction user, i.e. the SIP Registrar core, through the gates from\_tu and to\_tu. The gates pin and pout are used for communication with the environment, i.e. to receive REGISTER requests and to send proper responses.

Since LOTOS does not include state-variables, the state machine is implemented as a recursive process where the current state is maintained in a parameter of this process.

Fig. 8. State machine for handling transactions of a Session Initiation Protocol Registrar (Source: [RSC<sup>+</sup>02]).

Every time the process is invoked it checks its current state and reacts according to Figure 8.

In addition to the current state parameter trans\_state (Line 2), which may have the value ts\_trying, ts\_completed, or ts\_terminated, the process takes two further parameters: branch (Line 3), which is used to identify retransmissions; response (Line 4), which holds the last sent response.

As indicated by the **noexit** keyword (Line 4), this server process does not terminate, but continues forever. Thus, as an abstraction we can only have one transaction state machine. The state machine is never destroyed, but only the relevant parameters are reset once the terminated state is entered.

If the model of the state machine is in the *Terminated*-state, it waits to receive a message and moves on to the *Trying* state if a message is received. The reception of REGISTER messages (and some initial validations) is modeled by the process <code>listenForMessage</code> (Line 7). On successful termination the process <code>listenForMessage</code> passes the control to the succeeding behavioral block (>> operator). If a valid message has been received, indicated by the <code>hand\_to\_tu</code> variable, then the request is forwarded to the transaction user (Line 11) and the state machine moves to the *Trying*-state (Line 13).

If the state machine is in the *Trying*-state (Line 23), any response from the transaction user (Line 24) is sent to the environment of the Registrar (Line 25). After that the state machine moves on to the *Completed*-state (Line 27).

In the *Completed*-state there is a non-deterministic internal choice between receiving a retransmission (Lines 32-36) and finally moving to the *Terminated*-state (Line 42). This non-deterministic choice is an abstraction for the timeout transition in the state machine.

Note that this non-deterministic choice is not the only source of non-determinism within our specification. Another non-deterministic choice within the SIP Registrar specification deals with user authentication. This is a feature that is not necessarily

```

process serverTransaction [pin, pout, from_tu, to_tu](

1

trans_state: TransState,

2

branch: Branch.

3

response: SipResp) : noexit :=

4

5

[trans_state eq ts_terminated] -> (

6

7

listenForMessage[pin,pout,from_tu,to_tu](branch,response) >>

accept msg: RegisterMsg, resp: SipResp, hand_to_tu: Bool in

8

9

(

[hand_to_tu] \rightarrow (

10

11

to_tu !msg;

serverTransaction[pin, pout, from_tu, to_tu](

12

ts_trying, getBranch(msg) + 1, resp)

13

)

14

[]

15

[not(hand_to_tu)] \rightarrow (

16

serverTransaction[pin, pout, from_tu, to_tu](

17

ts_terminated, 0, resp)

18

)

19

)

20

)

21

[]

^{22}

[trans_state eq ts_trying] -> (

^{23}

^{24}

from_tu ?resp: SipResp;

25

pout !resp;

serverTransaction[pin, pout, from_tu, to_tu](

26

27

ts_completed, branch, resp)

)

^{28}

٢٦

29

[trans_state eq ts_completed] -> (

30

31

(

^{32}

i;

pin ?msg: RegisterMsg [(getBranch(msg) eq branch)];

33

pout !response;

34

serverTransaction[pin, pout, from_tu, to_tu](

35

ts_completed, branch + 1, response)

36

)

37

[]

38

39

(

40

i;

serverTransaction[pin, pout, from_tu, to_tu](

41

42

ts_terminated, 0, response)

)

43

)

44

45 endproc

```

Fig. 9. LOTOS specification of the transaction handling state machine of a Session Initiation Protocol Registrar.

turned on in a SIP Registrar. As we do not want to have two similar specification that just differ in the authentication handshake we have a non-deterministic choice between the authenticated and the unauthenticated mode of a SIP Registrar.

According to the RFC [RSC<sup>+</sup>02] a SIP Registrar may reject a message with a short expiration interval or it may accept this message. This requirement again introduces some non-determinism in our SIP Registrar model.

#### 3.2 Simplifications

As one can already see from the LOTOS example above, modeling always includes choosing proper simplifications. Although modern specification languages have high expressive power, it is impractical and often infeasible to model the complete concrete behavior of a system. Thus, when developing a formal model one usually abstracts from the real world.

Basically we distinguish between two different types of simplifications: *abstractions* and *limitations*. Abstractions are simplifications that preserve conformance. For example, one may only specify the behavior for a particular set of inputs; for the unspecified inputs the systems may behave arbitrarily. Hence, in the context of **ioco** with partial models, abstraction may constrain the inputs and may remove constraints from the output behavior. In contrast, a limitation is a restriction of the system's possible reactive behavior (output) and hence not a proper abstraction. Consequently, limitations do not preserve conformance and the tester must be careful in interpreting a fail verdict: it might be due to a limitation in the model.

In model-based testing the simplifications influence the kind of detectable faults. The more abstract or limited a formal model is, the less information for judging on the correctness of an implementation is available [Gau95]. Thus, a major challenge in deriving models for industrial applications is the selection of proper simplifications. Simplifications need to limit a specification's state space to a manageable size, while the model still needs to be concrete enough to be useful.

According to [PP05, PPW<sup>+</sup>05] we distinguish five classes of abstractions: functional, data, communication, temporal, and structural abstractions. Functional abstraction focuses on the functional part of the specification. This class of abstractions comprises the omission of behavior that is not required by the objectives of the model. Data abstraction subsumes the mapping from concrete to abstract values. Data abstraction includes the elimination of data values that are not needed within the functional part of the specification. Communication abstraction maps complex interactions to a more abstract level, e.g., the formal model uses one message to abstract a handshake scenario (several messages) of the real world. Temporal abstraction deals with the reduction of timing dependencies within the formal specification. For example, a certain model specifies only the ordering of events, but abstracts from discrete time values. Structural abstraction combines different real world aspects into logical units within the model.

**Simplifications for the SIP Registrar Model** When developing the formal model of a SIP Registrar we have chosen the simplifications listed in Table 2.

In particular, we simplify our model with respect to general server errors (Simplification 1), because of the loose informal specification of server errors within the RFC. Server errors may occur at any time when the Registrar encounters an internal error. For testing general server errors we would need a significant knowledge about the implementation internals. Especially, in order to trigger a server error during test execution, we would need to know how to enforce it. Hence, we skip server errors from the modeled behavior which may result in a wrong testing verdict. Therefore, this simplification is a limitation.

Simplification 2 omits specification details about forwarding requests. Thus, we

| id | type       | description                                                                                                                                     |

|----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | limitation | Our formal model of the Registrar never terminates with a server error.                                                                         |

| 2  | limitation | Our specification never forwards REGISTER messages to other SIP Reg-<br>istrars.                                                                |

| 3  | limitation | We assume that the communication channel is reliable and delivers mes-<br>sages in the sent order.                                              |

| 4  | functional | The Registrar starts from a well known initial state.                                                                                           |

| 5  | functional | While the authentication handshake is in our model, the calculation of authentication credentials is not modeled.                               |

| 6  | functional | REGISTER messages do not contain any REQUIRES header fields.                                                                                    |

| 7  | data       | The CALL-ID is abstracted to the range $[0, 1]$ .                                                                                               |

| 8  | data       | We limit the integer part of the CSEQ header to $[0, 1]$ . The method part is not in the formal model.                                          |

| 9  | data       | The range $[0, 2^{32-1}]$ of the EXPIRES header field can be divided into three partitions where we use only boundary values of each partition. |

| 10 | data       | Our model uses three different users: An authorized user, a known but<br>unauthorized user and an unknown user.                                 |

| 11 | data       | Our formal model uses three different CONTACT values: *, any_addr1, and any_addr2.                                                              |

| 12 | data       | The To and FROM header fields are omitted in our abstract REGISTER messages.                                                                    |

| 13 | temporal   | Our specification does not use any timers. We only focus on the ordering of events.                                                             |

Table 2. Simplifications for the specification of the SIP Registrar.

do not generate tests for this feature. This is again a limitation as the forwarding of requests would result in different outputs, i.e. the receiver of the forwarded request responds to the REGISTER message.

Simplification 3 removes the needs for modeling possible interleaving of messages. During test execution this assumption is ensured by running the test execution framework and the implementation under test on the same computer.

Simplification 4 requires the start from a defined initial state. Otherwise, our model would have to consider different database contents on startup of the Registrar. We consider this a functional abstraction, because the functionality for other initializations is left open.

Simplifying the model with respect to the calculation of authentication credentials (Simplification 5) does not impose any limitation if the credentials are calculated and inserted correctly into test messages during test execution. As the detailed algorithm for credentials calculation is abstracted this is a functional abstraction.

We also skipped the REQUIRES header field in the formal specification in order to limit the number of possible request messages (Simplification 6). Not considering this input header field as being part of a REGISTER request represents a functional abstraction: the implementation may behave arbitrarily after this unspecified request.

Simplifications 7-10 are based on the ideas of equivalence partitioning and boundary value analysis [Mye79], which are strategies from white-box testing. For example, Simplification 10 uses the fact, that the Registrar relevant part of the RFC only distinguishes users that (1) are known by the proxy and allowed to modify contact information, (2) that are known by the proxy but are not allowed to modify contact information, and (3) users that are not known by the proxy, i.e. users that do not have an account. Thus, only three different users are needed, one of each group. Note that the simplifications 7-10 are data abstractions. Each of the header fields addressed by these abstractions are inputs to our specification. However, as we have one value per equivalence partition this is not a functional abstraction: every behavior (with respect to these inputs) of the system is modeled. Nevertheless, as we do not model all possible input values this is a data abstraction.

Simplification 11 limits the different CONTACT header field values. We allow the two addresses "any\_addr1" and "any\_addr2", respectively. These two elements are replaced during test execution with valid contact addresses. According to the RFC, the asterisk is used for "delete" requests. This is again a data abstraction as the different possible behaviors are covered by our specification.

Simplification 2 causes the header fields, To and FROM, to contain redundant information. So they can be omitted from our formal REGISTER messages (Simplification 12). Again this is a data abstraction.

Finally, as TGV does not support real-time testing, we need to abstract from concrete time events (Simplification 13).

## 4 Fault-based Conformance Testing

Given a formal specification there is a huge, possibly infinite, number of test cases that can be derived from that specification. There are different ways of selecting a finite set of test cases. One possibility for test case selection is the use of coverage criteria (e.g. [CR93, FWW08a]) on the level of the specification. Another way is the use of anticipated faults for the generation of test cases. This idea dates back to the late 1970s [DLS78, Ham77] where testers mutated source code to assess their test cases. Budd and Gopal [BG85] applied this technique to specifications.

In this paper, we also consider specification mutation as a way to select test cases. A fault is modeled at the specification level by altering the specification syntactically. The idea is to generate test cases that would fail if an implementation conforms to a faulty specification [AD06]. In order to generate test cases we mutate LOTOS specifications. Every mutant is compared to the original specification with respect to input-output conformance. If the mutant does not conform to the specification, then the trace leading to non-conformance serves as a test purpose. This test purpose is fed into the TGV tool [JJ05] in order to derive tree structured test cases which can be applied to non-deterministic systems.

Thus, we generate a test purpose for a specification S as follows:

- 1. Select a mutation operator  $O_m$ .

- 2. Generate a mutated version  $S^m$  of the specification S by applying  $O_m$  to S.

- 20 International Journal of Software and Informatics, Vol.XX, No.XX, XXXXXX 20XX

- 3. Check S and  $S^m$  for input output conformance (using an ioco checker [WW08a]).

- 4. Use the counterexample c, if any, as a test purpose  $TP^1$  for the TGV tool.

- 5. Run the TGV tool with the test purpose TP on the original specification S in order to derive the final test case.

As we introduce faults at the level of the specification mutation operators are needed. These operators represent the sort of faults that we consider. For the selection of mutation operators one usually relies on two hypotheses [BDLS80]. The first one is called the 'competent specifier hypothesis' which is related to the 'competent programmer hypothesis' [BDLS80]. This hypothesis states that the specifier (programmer) is usually competent and gets the specification (program) almost correct. Faults can be corrected by a few key strokes.

The second assumption is called the 'coupling hypothesis'. It states, that big and dramatic effects that arise from bugs in software are closely coupled to small and simple failures.

Due to these two assumptions we can stick to small mutations on the specification. Thus, as usual in mutation testing, we use small syntactic changes on LOTOS specifications; each mutant only comprises a single mutation.

We use some of the mutation operators proposed in [BOY00, SCSP03] and adapted them to LOTOS specifications. Our mutation operators listed in Table 3.

# 4.1 Fault-based IOCO Testing

We are interested in testing for input-output conformance. Thus, for every mutant we want to generate a test case, such that the test case fails if this mutant has been implemented. However, not all mutation operators lead to models that can be distinguished from the original specification when using **ioco**, i.e. not all mutations represent faults. A fault can only be defined with respect to a conformance relation.

A mutant that cannot be distinguished from the original specification is called equivalent mutant. Although, the **ioco** relation is not an equivalence relation, we still use the terms equivalent and non-equivalent mutant as they are common in mutation testing. For an equivalent mutant there is no test case that distinguishes the mutant from the original specification. Contrary, a non-equivalent mutant comprises a fault such that there is a test case that passes on the original specification and fails on the mutant.

In the following the meaning of faults in the context of **ioco** is shown. Our first observation is that not all injected faults will cause observable failures. In order to observe a failure, the mutant must not conform (with respect to **ioco**) to our original specification. Hence, given an original specification S we are only interested in mutants  $S^m$ , such that<sup>2</sup>

$$\neg (S^m \text{ ioco } S)$$

Unfolding the definition of **ioco** gives

$$\neg \ (\forall \sigma \in Straces(S) \bullet out(S^m \text{ after } \sigma) \subseteq out(S \text{ after } \sigma))$$

(1)

$<sup>^{1}</sup>$  The labels of the test processes are marked with *INPUT* or *OUTPUT*. We remove these marks. Furthermore, we have to add Refuse and Accept states.

<sup>&</sup>lt;sup>2</sup> We make  $S^m$  input enabled.

| Op. | Name                            | Description                                                                                                                                                                                                  |

|-----|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASO | Association Shift Op.           | Change the association between variables in boolean expressions, e.g. replace $x \land (y \lor z)$ by $(x \land y) \lor z$ .                                                                                 |

| CRO | Channel Replacement Op.         | Replace the communication channel, i.e<br>change the gate of an event. For example, this<br>operator would change Line 34 of Figure 9<br>from pout !response to pin !response.                               |

| EDO | Event Drop Op.                  | Drop events of the specification.                                                                                                                                                                            |

| EIO | Event Insert Op.                | Duplicate existing events.                                                                                                                                                                                   |

| ENO | Expression Negation Op.         | Replace an expression by its negation, e.g. replace $x \wedge y$ by $\neg(x \wedge y)$ .                                                                                                                     |

| ERO | Event Replacement Op.           | Replace an event by a different event. For example, applying this operator to Line 34 o Figure 9 leads to pout !response to pout.                                                                            |

| ESO | Event Swap Op.                  | Swap two neighbouring events.                                                                                                                                                                                |

| HDO | Hiding Delete Op.               | Delete an event from hide definition, i.e. make<br>an unobservable event observable.                                                                                                                         |

| LRO | Logical Operator Replacement    | Replace a logical operator by other logical operators.                                                                                                                                                       |

| MCO | Missing Condition Op.           | Delete conditions from decisions.                                                                                                                                                                            |

| ORO | Operand Replacement Op.         | Replace an operand (variable or constant) by<br>another syntactically legal operand, e.g. or<br>mutation with respect to this operator is to<br>replace the branch variable in Line 33 of Fig<br>ure 9 by 0. |

| POR | Process Operator Replacement    | Replace synchronization operators (  , [] ,                                                                                                                                                                  |

| PRO | Process Replacement Op.         | Replace process instantiations with stop or<br>exit events                                                                                                                                                   |

| RRO | Relational Operator Replacement | Replace a relational operator $(<, \leq, >, \geq, = \neq)$ by any other except its opposite (since the opposite is similar to the negation operator)                                                         |

| SNO | Simple Expression Negation      | Replace a simple expression by its negation<br>e.g. negate $x$ in $x \wedge y$ getting $(\neg x \wedge y)$ .                                                                                                 |

| SOR | Sequential Operator Replacement | Replace the sequential composition operator<br>>> and [>.                                                                                                                                                    |

| USO | Unobservable Sequence Op.       | Make events of the specification unobservable                                                                                                                                                                |

Table 3. Mutation operators for LOTOS specifications.

which can further be rewritten to

$$= \exists \sigma \in Straces(S) \bullet out(S^m \text{ after } \sigma) \not\subseteq out(S \text{ after } \sigma)$$

(2)

This is the first hint for a testing strategy. We are interested in the suspension trace of actions leading to non-conformance between the mutant and the original LTS. In other words, our test purposes for detecting faults are sequences of actions leading to non-conformance. As one can see from this formula, a non-conformance check can be reduced to a test for subsets on the output labels.

It follows that a failure is observed, if the mutant  $S^m$  produces an output o not predicted by specification S:

$$= \exists \sigma \in Straces(S) \bullet \exists o \bullet o \in out(S^m \text{ after } \sigma) \land o \notin out(S \text{ after } \sigma)$$

$$(3)$$

This simple derivation shows an important property of the **ioco** relation: mutating the specification by injecting an additional input a such that a new trace for the mutant  $S^m$  is generated, i.e.  $\forall \sigma \in Straces(S) \bullet \sigma \cdot a \notin Straces(S)$ , does not lead to a failure.

The theory highlights a further important clarification in fault-based testing: In the presence of non-determinism, there is no guarantee that an actual fault will always be detected. The reason is that non-conformance only means that there is a wrong output after a trace of actions, but the implementation may still opt for the correct one. In that case we rely on the complete testing assumption [LvBP94], which says that an implementation exercises all possible execution paths of a test case t, when tis applied a predetermined finite number of times.

## 4.2 On-the-fly IOCO Checking

As highlighted above we only need to consider mutants  $S^m$  of a specification S such that  $\neg(S^m \text{ ioco } S)$ . Because the state spaces of specifications are usually huge, we cannot construct the state space of the specification and the mutant in advance, and then check for conformance. Thus, conformance checking between the mutant and the specification has to be done on the fly.

Therefore, we use the LOTOS parser of the CADP toolbox [GLM02]. This parser takes a LOTOS specification and allows one to access the underlying LTS incrementally. The LOTOS specification is translated into an initial-state and a successor-function. The successor-function takes a state and returns the edges, i.e. labels and end-states, that are enabled in the given state.

In order to check two labeled transition systems for conformance we use an approach similar to the approach of Fernandez and Mounier [FM91]. That is, we define a synchronous product  $(\times_{ioco})$  between two labeled transition systems  $S^m$  and S such that  $S^m \times_{ioco} S$  contains special fail states if  $\neg(S^m \text{ ioco } S)$ . Checking for conformance is then implemented as a simple reachability search for fail states. If there is a fail state after a particular path, then this path is a counter-example showing the non-conformance between  $S^m$  and S.

Since, the input output conformance relation uses  $\delta$ -labeled transitions and these transitions are not initially provided by the semantics of LOTOS specification we have to identify and to label quiescent states before calculating the synchronous product. More precisely, we add quiescence labeled transitions for quiescent states when iterating over the transitions of a particular state.

After adding the quiescence information we make the two labeled transition systems deterministic. This is done during the calculation of the synchronous product by the use of the subset construction [HU79]. Note that in the worst case this may cause an exponential increase of the number of states. During the process of making the LTSs deterministic we remove  $\tau$ -labeled transitions too.

**Definition 14.** Let  $S^m = (Q^{S^m}, L \cup \{\tau, \delta\}, \rightarrow_{S^m}, q_0^{S^m})$  and  $S = (Q^S, L \cup \{\tau, \delta\}, \rightarrow_S, q_0^S)$  be two deterministic LTSs, where the labels L are partitioned into inputs  $L_I$

and outputs  $L_U$ , i.e.  $L = L_I \cup L_U$  and  $L_I \cap L_U = \emptyset$ . The synchronous product  $SP = S^m \times_{ioco} S$  is an LTS  $SP = (Q^{SP}, L, \rightarrow_{SP}, q_0^{SP})$ , where its state set  $Q^{SP}$  is a subset of  $(Q^{S^m} \times Q^S) \cup \{pass, fail\}$  reachable from the initial state  $q_0^{SP} =_{df} (q_0^{S^m}, q_0^S)$  by the transition relation  $\rightarrow_{SP}$ . Let  $q^{S^m} \in Q^{S^m}$  and  $q^S \in Q^S$  be two states of  $S^m$  and S, respectively. Then, the transition relation  $\rightarrow_{SP}$  is defined as the smallest set obtained by the application of the following rules:

- 1. Edges possible in both LTSs,  $S^m$  and S:  $\forall a \in L_I \cup L_U \bullet \forall q'^{S^m} \in Q^{S^m}, q'^S \in Q^S \bullet q^{S^m} \xrightarrow{a}_{S^m} q'^{S^m} \wedge q^S \xrightarrow{a}_S q'^S \Rightarrow (q^{S^m}, q^S) \xrightarrow{a}_{SP} (q'^{S^m}, q'^S).$

- 2. Implementation freedom on unspecified inputs:  $\forall a \in L_I \bullet \forall q'^{S^m} \in Q^{S^m} \bullet q^{S^m} \xrightarrow{a}_{S^m} q'^{S^m} \wedge q^S \xrightarrow{a}_{S} \Rightarrow (q^{S^m}, q^S) \xrightarrow{a}_{SP} pass.$

- 3.  $S^m$  may allow fewer outputs than S:  $\forall b \in L_U \bullet \forall q'^S \in Q^S \bullet q^S \xrightarrow{b}_S q'^S \land q^{S^m} \xrightarrow{b}_{S^m} \Rightarrow (q^{S^m}, q^S) \xrightarrow{b}_{SP} pass.$ 4. Input enabledness of  $S^m$ :

- $\forall a \in L_I \bullet \forall q'^S \in Q^S \bullet q^S \xrightarrow{a}_S q'^S \land q^{S^m} \xrightarrow{a}_{S^m} \Rightarrow (q^{S^m}, q^S) \xrightarrow{a}_{S^P} (q^{S^m}, q'^S).$

- 5. Unspecified outputs of  $S^m$ :  $\forall b \in L_U \bullet \forall q'^{S^m} \in Q^{S^m} \bullet q^{S^m} \xrightarrow{b}_{S^m} q'^{S^m} \land q^S \xrightarrow{b}_{S} \Rightarrow (q^{S^m}, q^S) \xrightarrow{b}_{SP} fail.$

Rule 1 states, that edges that are possible in both LTSs are edges of the synchronous product.

Rule 2 handles the cases where the LTS representing the implementation allows inputs, that are not specified by the LTS representing the specification. Since **ioco** allows any behavior on unspecified inputs we add a pass state to the synchronous product. The added state is a sink state, i.e., there are no outgoing edges. Note, that pass states do no affect the final comparison result, since only the existence of fail states determine whether two LTS are related under conformance (with respect to **ioco**) or not.

Since, **ioco** requires that the outputs of the implementation's LTS have to be a subset or have to be equal to the outputs of the specification's LTS we add an edge to a pass state for any output that is allowed in S but not in  $S^m$  (Rule 3). Again, this pass state has no influence on the final comparison result.

Note, that **ioco** requires the left hand side LTS to be weakly input enabled. In practice this may not be the case for a given input output labeled transition system. Thus, we have to convert the left hand side LTS to a weakly input enabled LTS. The synchronous product considers this requirement by Rule 4 of the transition relation. This rule assumes that an input is always possible in  $S^m$ . Thus, if input *a* is not allowed in  $S^m$ , the input enabledness allows to assume a self-loop labeled with *a* on state  $q^{S^m}$ . Hence, this rule ensures that the synchronous product will not contain an edge leading to fail because  $S^m$  lacks input enabledness.

We add an edge leading to a fail state if an output of the left hand LTS  $S^m$  is not an output of the right hand LTS S (Rule 5). Only in that case the two LTSs do not conform with respect to **ioco**.

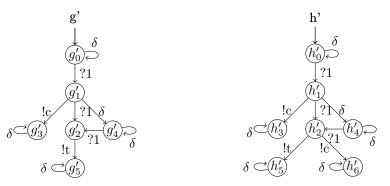

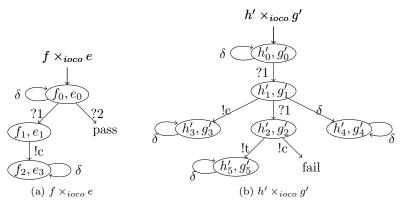

**Example 9.** Figure 11 shows the synchronous products used to check conformance

Fig. 10. Deterministic versions of the labeled transition systems g and h of Figure 3.

Fig. 11. Synchronous products illustrating the application of Definition 14 to the labeled transition systems f and e of Figure 3 and g' and h' of Figure 10.

on some of the labeled transition systems of Figure 3. The basis of the **ioco** check are  $\delta$ -annotated deterministic labeled transition systems.

When checking f **ioco** e the synchronous product according to Definition 14 looks like the LTS shown in Figure 11a. The trace  $\langle ?2 \rangle$  of the implementation's model f is not relevant in specification e, and hence Rule 2 of Definition 14 applies.

When checking g ioco h and h ioco g the two labeled transition systems are turned deterministic first. The resulting LTSs g' and h' are illustrated in Figure 10. The synchronous product using  $\times_{ioco}$  is illustrated in Figure 11b.

The fail state comes from Rule 5 which says, that outputs of the implementation that are not allowed by the specification lead to fail. However, when checking the reverse relation g **ioco** h there would be a pass state instead of the fail state. This is because implementations may have fewer outputs than specifications after a particular trace (Rule 3).

As the synchronous products are constructed on-the-fly the construction stops if a fail-state is reached.  $\hfill \Box$

## 4.3 Handling large state spaces

IOCO checking of two conforming labeled transition systems requires the comparison of their whole state spaces. For large industrial specifications this is often infeasible. In the case of our SIP Registrar specification, the attempt of constructing the Fault-based Conformance Testing in Practice

specification's state space on a computer with 2GB RAM failed after 11 days due to insufficient memory. Note that for this experiment we bound all used data types of our specification.

To overcome this problem, we proposed to exploit the knowledge where the fault has been inserted in the LOTOS specification [APWW07a]. By marking the place of the mutation it is possible to construct the relevant part of the state space only, i.e. the part that reflects the mutation. However, since the position of the markers is determined syntactically, our approach is not applicable for all mutation operators. For example, for the SIP Registrar specification, we succeeded to mark 252 out of 843 mutants only, i.e. our approach applied to only 30% of the mutants [AWW08].

Nevertheless, the on-the-fly approach for checking the conformance of two specifications is suitable for any mutation operator. We can apply the conformance check not to the whole specification's state space but only up to a particular depth. Thus, similar to bounded model checking  $[BCC^+03]$ , we check for bounded input-output conformance:

**Definition 15 (Bounded input-output conformance).** Given a set of inputs  $L_I$  and a set of outputs  $L_U$  then  $\mathbf{ioco}^{|k|} \subseteq \mathcal{IOTS}(L_I, L_U) \times \mathcal{LTS}(L_I, L_U)$  is defined as:

$$\begin{split} IUT \ \mathbf{ioco}^{|k|} \ S =_{df} \forall \sigma \in Straces(S) \bullet \\ (length(\sigma) \leq k) \implies (out(IUT \ \mathbf{after} \ \sigma) \subseteq out(S \ \mathbf{after} \ \sigma)) \\ \Box \end{split}$$

**Example 10.** For example, let the input output transition system k of Figure 4 be the specification and let the IOTS l of Figure 4 be the model of an implementation. l does not (ioco-) conform to k, i.e.  $\neg(l \text{ ioco } k)$ , because  $out(l \text{ after } \langle ?1, \delta, ?1 \rangle) = \{!c, !t\} \not\subseteq \{!t\} = out(k \text{ after } \langle ?1, \delta, ?1 \rangle)$ . However, we have l ioco<sup>[0]</sup> k, because  $out(l \text{ after } \langle \rangle) = \{\delta\} = out(k \text{ after } \langle \rangle)$ . Furthermore, we have l ioco<sup>[1]</sup> k, because l ioco<sup>[0]</sup> k, out(l after  $\langle \delta \rangle) = \{\delta\} = out(k \text{ after } \langle \delta \rangle), out(l \text{ after } \langle ?1 \rangle) = \{!c, \delta\} = out(k \text{ after } \langle ?1 \rangle), and out(l after <math>\langle ?2 \rangle) = \{\delta\} = out(k \text{ after } \langle ?2 \rangle)$ . We also have l ioco<sup>[2]</sup> k, because l ioco<sup>[0]</sup> k and l ioco<sup>[1]</sup> k and there is no trace after which an output of l is not allowed by k. The shortest trace leading to non-conformance has a length of three, i.e.  $\langle ?1, \delta, ?1 \rangle$ . Thus, with a bound greater or equal to three l does not conform to k, i.e.  $\neg(l \text{ ioco}^{[3]} k)$ .

In contrast to our previous syntactic labelling technique, bounded input-output conformance checking applies to any mutation operator. If we find a counter-example when checking for  $S^m \operatorname{ioco}^{|k|} S$  within a particular bound k, then the counter-example is also valid for showing non-conformance for ioco. However, failing to show non-conformance within a particular bound k does not mean that we necessarily have an ioco-correct, i.e. an equivalent, mutant. Thus, the technique is sound but incomplete. Here, soundness guarantees that no counterexamples for equivalent mutants are generated. Hence, we will never produce redundant test cases from equivalent mutants. Due to incompleteness we may miss some test cases aiming for faults that are observable only above the boundary.

|     | No.pro- | No.ac- | No.data-            | net. Li | ines of Code |

|-----|---------|--------|---------------------|---------|--------------|

|     | cesses  | tions  | $_{\mathrm{types}}$ | Total   | data types   |

| SIP | 10      | 27     | 20                  | 3000    | 2500         |